#### Sub GHz band short range wireless transceiver IC

# ■GENERAL DESCRIPTION

The ML7396 family (ML7396A (915MHz band), ML7396B (920MHz band), and ML7396E (868MHz band)) are ICs for transmitting/receiving data which integrate the RF, IF, MODEM and HOST interface sections into one chip for the specified low power radio communication. The ML7396 family is used for FCC PART15, ARIB STD-108(specified low-power radio station, 920MHz-band telemeter, telecontrol and data transmission radio equipment), ETSI EN 300 220 compliant radio station, and uses a packet transmission function of IEEE802.15.4d and IEEE802.15.4g.

# ■FEATURES

- Compliant to ARIB STD T-108 (ML7396B)

- Compliant to FCC Part15 (ML7396A)

- Compliant to ARIB STD T-108 ETSI EN 300-220 (ML7396E)

- High accurate modulation implemented by direct modulation scheme using fractional-N PLL.

- Modulation : GFSK / GMSK, FSK / MSK

- (MSK is FSK transmission of modulation degree: m=0.5)

- Data rates: 10 / 20 / 40 / 50 / 100 / 150 / 200 kbps and 400 kbps(option)

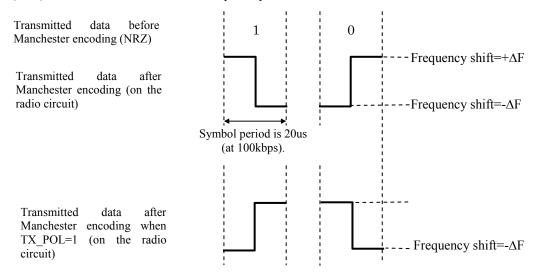

- Data coding: NRZ and Manchester codes

- Applicated channel filter suited to data transmission speed

- Programmable modulation frequency shift

- Polar conversion for TX and RX data bits

- 36MHz oscillator

- TCXO direct inputs available

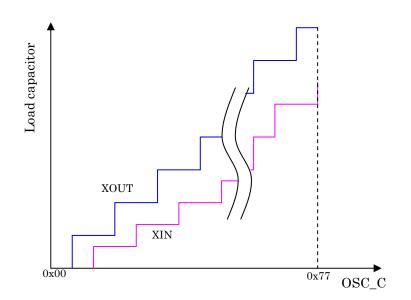

- load capacitance control function of oscillation circuit

- Frequency trimming function (frequency fine tuning by oscillation circuit and fractional-N PLL)

- Host interface: SPI

- Built-in power amplifier (PA) with output power control function (output power select function among 20mW/10mW/1mW, trimming function)

- External PA control

- Receive Signal Strength Indicator (RSSI) reporting function and threshold comparison function

- AFC function at RX

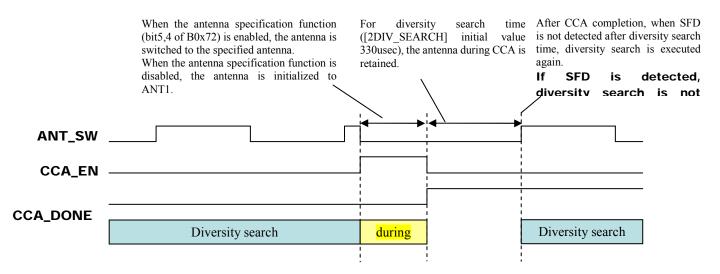

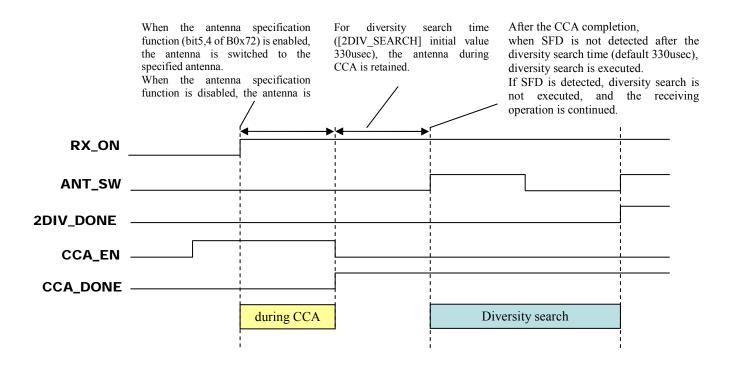

- Support 2 antenna diversity

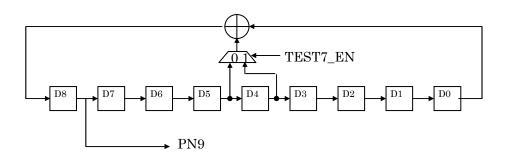

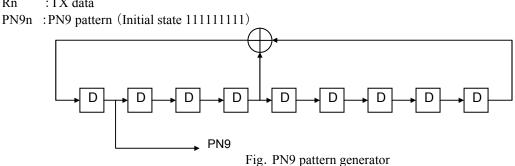

- Test pattern generator(PN9, CW, 01 pattern, all-1s, all-0s)

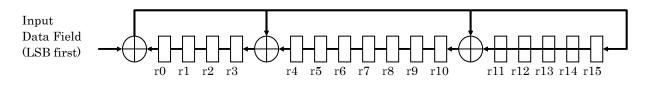

- FEC function

- IEEE802.15.4d/g support

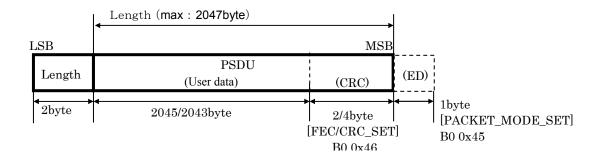

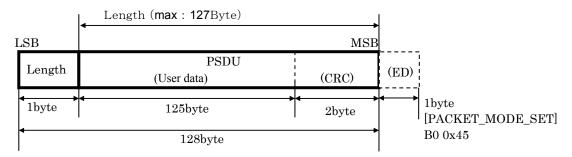

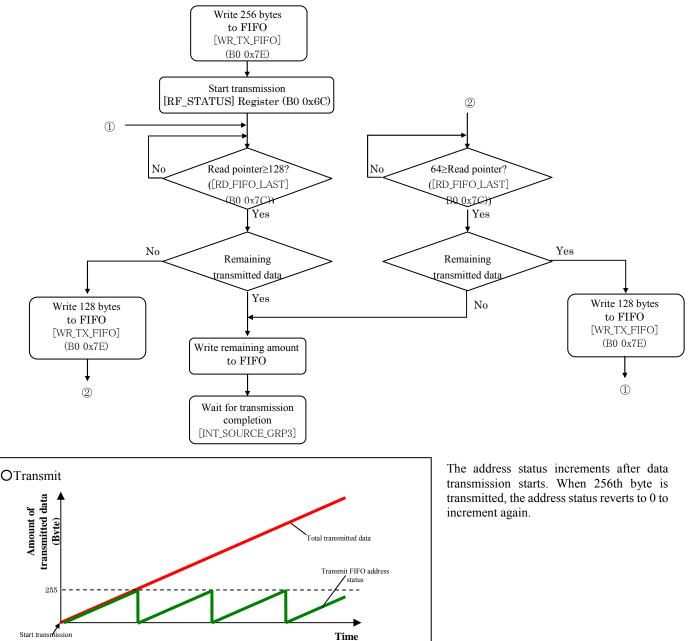

- Separate 256-byte TX and RX buffers

- o Max packet length 2047Byte (IEEE802.15.4g case)

- Preamble pattern detection function (Preamble length can be prgrammable between 1 to 15 Byte)

- Programmable TX preamble length (Max 255 Byte)

- SFD detection function (Max 4 Byte, available for TX and RX)

- o CRC function (CRC32, CRC16-IBM, CRC16, CRC8 or no-CRC)

- Whitening function

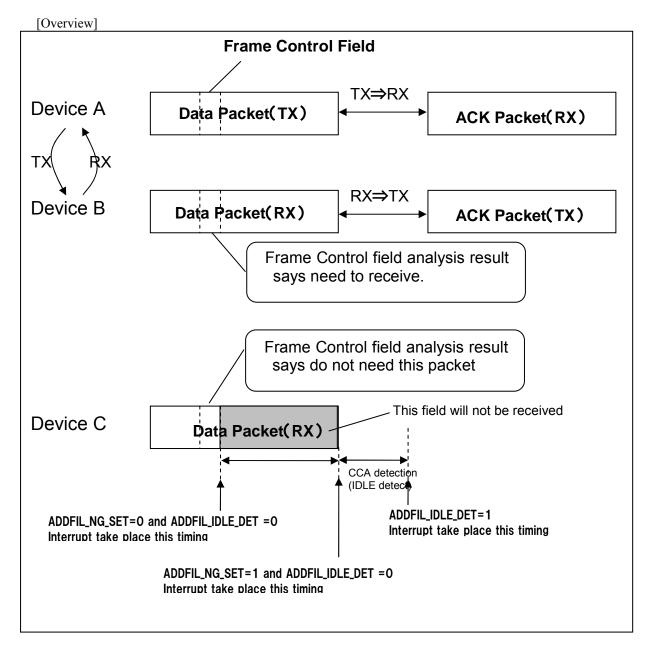

- Address filtering function

- o Automatic Acknowledge (Ack TX or RX) function

- o FEC function (with IEEE802.15.4g mode)

### LAPIS Semiconductor Co.,Ltd.

| <ul> <li>Power supply:</li> </ul> | 1.8 to 3.6V (TX power 1mW mode)                            |

|-----------------------------------|------------------------------------------------------------|

|                                   | 2.3 to 3.6V (TX power 10mW mode)                           |

|                                   | 2.6 to 3.6V (TX power 20mW mode)                           |

| Operating tempe                   | rature: $-40$ to $+85$ deg.C                               |

| Power consumpt                    | ion (920MHz)                                               |

| Sleep mo                          | de $0.9 \ \mu \text{ A}$ (Typ.) (registor value retention) |

| T 11                              |                                                            |

| Idle mo | ode  | 1.4mA (Typ.)     |         |

|---------|------|------------------|---------|

| ΤX      | 20mW | 32 mA (Typ.)     |         |

|         | 10mW | 24 mA (Typ.)     |         |

|         | 1mW  | 13 mA (Typ.)     |         |

| RX      |      | 15 mA (Typ.) (@1 | 00kbps) |

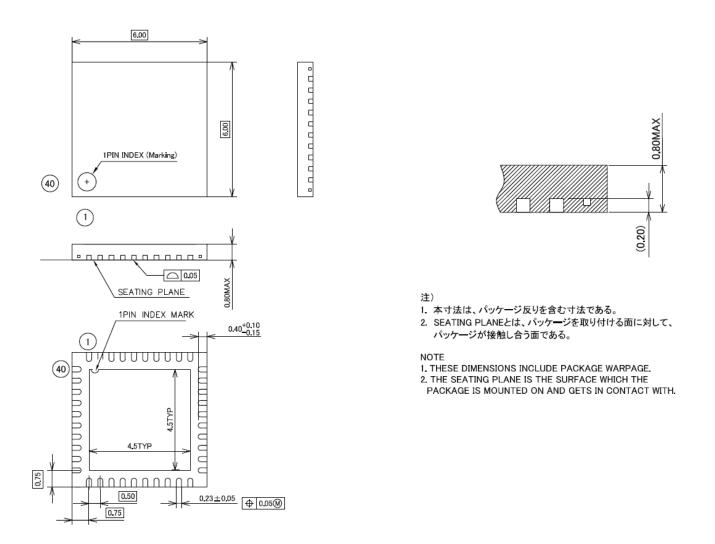

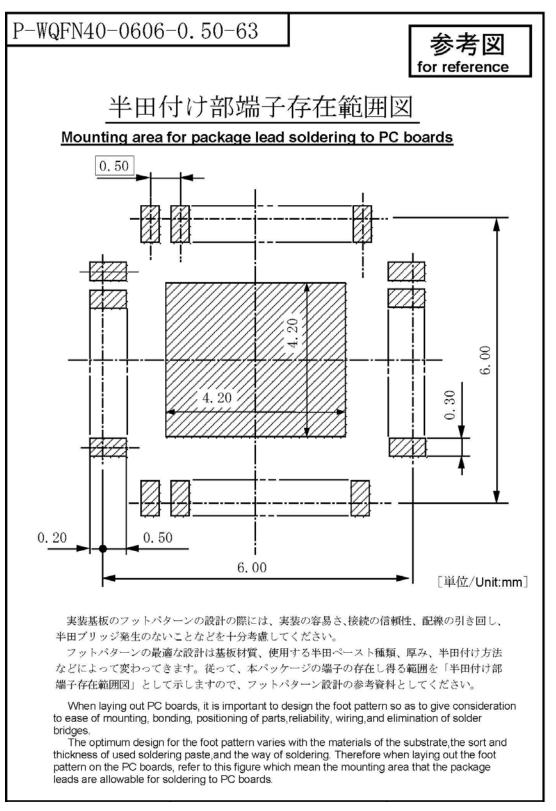

• Package

40 pin WQFN P-WQFN40-0606-0.50 Pb free, RoHS compliant

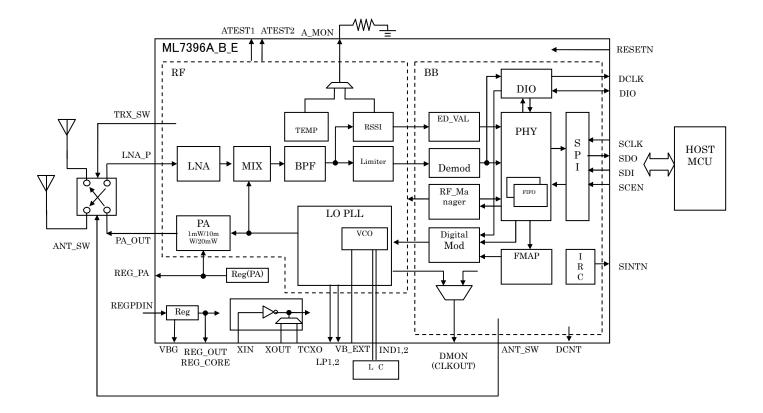

# ■BLOCK DIAGRAM

Fig.2-1 Block diagram

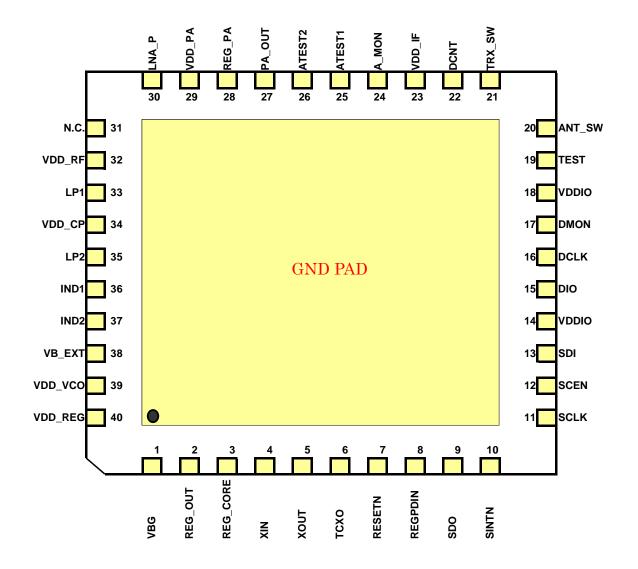

## ■PIN ASSIGNMENT

•Pin Location

NOTE) Pattern shown in the centre of the chip is located at bottom side of the chip (GND PAD)

# ■PIN DEFINITION

### Symbols

| I <sub>RF</sub> : RF input |  |

|----------------------------|--|

|----------------------------|--|

- $O_{RF} \quad \ \ : RF \ output$

- I<sub>A</sub> : Analog input

- I<sub>OS</sub> : Oscillator input

- Oos : Oscillator output

- I : Digital input

- O : Digital output

- Is : Shmidt Trigger input

### •RF part

| Pin name | Pin<br>No | Direction       | Active<br>Level | Dir/state<br>at reset | Detail function                                                           |  |

|----------|-----------|-----------------|-----------------|-----------------------|---------------------------------------------------------------------------|--|

| LNA_P    | 30        | I <sub>RF</sub> | -               | Ι                     | RF antenna input                                                          |  |

| PA_OUT   | 27        | O <sub>RF</sub> | -               | 0                     | RF antenna output                                                         |  |

| IND1     | 36        | -               | -               | -/-                   | Pin for external inductor                                                 |  |

| IND2     | 37        | -               | -               | -/-                   | Pin for external inductor                                                 |  |

| LP1      | 33        | -               | -               | -/-                   | Pin for PLL loop filter                                                   |  |

| VB_EXT   | 38        | -               | -               | -/-                   | Pin for capacitor averaging internal bias                                 |  |

| ATEST1   | 25        | O <sub>RF</sub> |                 | Hi-Z                  | Test pin for IF and analog test circuit.<br>*Left open when in normal use |  |

| ATEST2   | 26        | O <sub>RF</sub> |                 | Hi-Z                  | Test pin for IF and analog test circuit                                   |  |

| A_MON    | 24        | O <sub>RF</sub> |                 | Hi-Z                  | Test pin for analog monitor, IF block and analog test circuit*1           |  |

[Description]

\*1 Analog monitor signal can be configured by register [RSSI/TEMP\_OUT] address (B1 0x03), no signal assigned as default condition.

### PIN DEFINITION(continued)

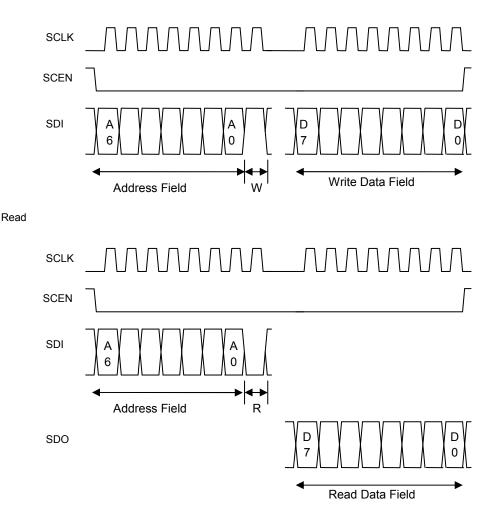

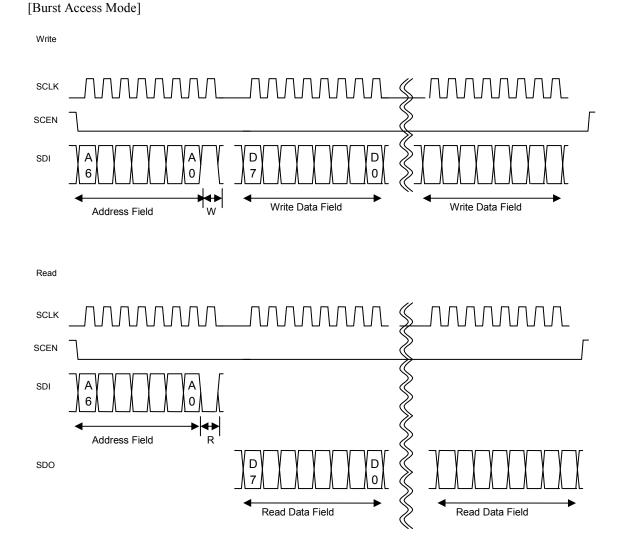

### •SPI interface

| Pin name | Pin<br>No | Direction | Active<br>Level | Dir/state<br>at reset | Detail function      |

|----------|-----------|-----------|-----------------|-----------------------|----------------------|

| SCLK     | 11        | Is        | P or N          | I/-                   | SPI clock input      |

| SCEN     | 12        | Is        | L               | I/-                   | SPI enable input     |

| SDI      | 13        | Is        | H or L          | I/-                   | SPI data input       |

| SDO      | 9         | О         | H or L          | O/L                   | SPI data output      |

| SINTN    | 10        | 0         | L               | O/H                   | SPI interrupt output |

### •DIO interface

| Pin name | Pin No | Direction | Active<br>Level | Dir/state at<br>reset | Detail function       |

|----------|--------|-----------|-----------------|-----------------------|-----------------------|

| DCLK     | 16     | 0         | P or N          | O/L                   | DIO clock output      |

| DIO      | 15     | I/O       | H or L          | O/L                   | DIO data input/output |

### •Regulator part

| Pin name | Pin No | Direction | Active<br>Level | Dir/state<br>at reset | Detail function                                                  |  |

|----------|--------|-----------|-----------------|-----------------------|------------------------------------------------------------------|--|

| REG_OUT  | 2      | -         | -               | -/-                   | Regulator output (typ.1.5V)<br>(Cap 10uF)                        |  |

| REG_PA   | 28     | -         | -               | -/-                   | Regulator output for PA block                                    |  |

| VBG      | 1      | -         | -               | -/-                   | External Capacitor pin (Cap 0.1uF)                               |  |

| REGPDIN  | 8      | Ι         | Н               | I/-                   | Power down pin for regulator<br>* Fix "L" when in normal use     |  |

| REG_CORE | 3      | -         | -               | -/-                   | Monitor pin for power supplyfor digita core(typ.1.5V) (Cap 10uF) |  |

# LAPIS Semiconductor Co., Ltd.

### PIN DEFINITION(continued)

### Miscellaneous

| Pin name | Pin<br>No | Direction      | Active<br>Level | Dir/state at<br>reset | Detail function                                                                                                                                                         |

|----------|-----------|----------------|-----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESETN   | 7         | Is             | L               | I/L                   | Hardware reset                                                                                                                                                          |

| XIN      | 4         | Ios            | P or N          | -                     | 36MHz crystal pin1<br>*Fixed to GND level when external clock<br>generator is used                                                                                      |

| XOUT     | 5         | Oos            | P or N          | -                     | 36MHzcristal pin2<br>*Fixed to GND level when external clock<br>generator is used                                                                                       |

| тсхо     | 6         | I <sub>A</sub> | -               | Ι                     | External clock (TCXO) input pin.<br>*Fixed to GND level when crystal<br>oscillator is used.                                                                             |

| TRX_SW   | 21        | О              | H or L or<br>OD | O/L                   | TX and RX switch signal<br>(0:RX /1:TX)                                                                                                                                 |

| ANT_SW   | 20        | О              | H or L or<br>OD | O/L                   | Diversity control signal                                                                                                                                                |

| TEST     | 19        | Ι              | Н               | I/-                   | Test mode input<br>Fixed to "L" when in normal use                                                                                                                      |

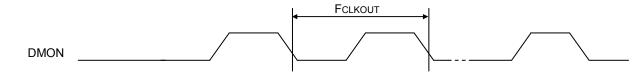

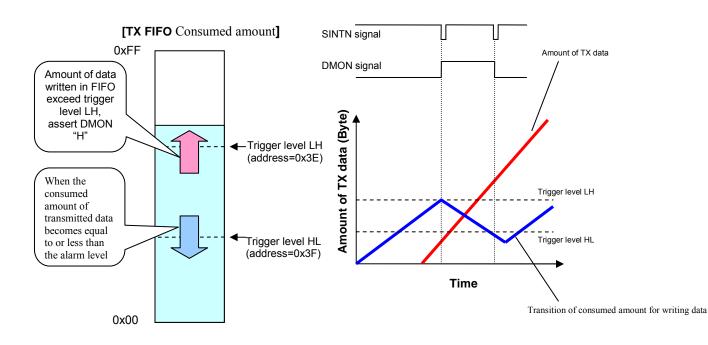

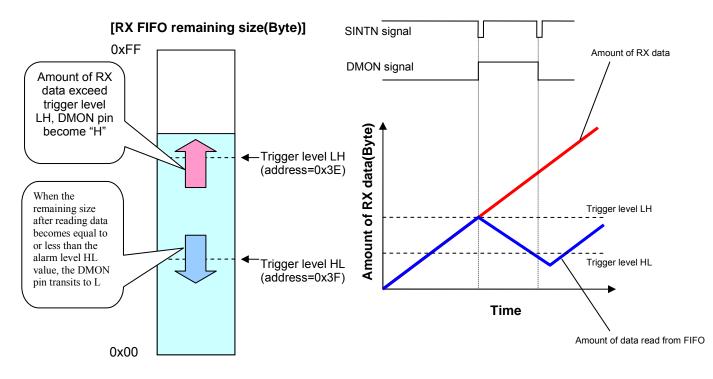

| DMON*1   | 17        | 0              | Н               | O/L                   | Monitor output pin for clock or digital<br>signals<br>Primary function: Clock output (6MHz)<br>Secondary function: PLL_LD output<br>Third function: FIFO trigger output |

| DCNT     | 22        | 0              | H or L or<br>OD | O/L                   | External PA control signal                                                                                                                                              |

| N.C.     | 31,35     | -              | -               | -                     | Non connection                                                                                                                                                          |

[Description]

\*1 Function of DMON pin can be selected by following condition. Clock output as a default. Please refer to each register description for more details. Primary function will have higher priority when multiple function are configured simultaneously.

| Function Name       | Configuration register name | Address | Bit position (bit symbol) |

|---------------------|-----------------------------|---------|---------------------------|

| CLK output          | CLK_SET                     | B0 0x02 | bit4 (CLKOUT_EN)          |

| PLL_LD output       | PLL_MON/DIO_SEL             | B0 0x69 | bit4 (PLL_LD)             |

| FIFO trigger output | CRC_AREA/FIFO_TRG           | B0 0x77 | bit0 (FIFO_TRG_EN)        |

### Configuration of DMON output

ML7396A/B/E

### •Power supply

| Pin name | Pin<br>No | Direction | Active<br>Level | Dir/state Detail function |                                               |

|----------|-----------|-----------|-----------------|---------------------------|-----------------------------------------------|

|          | INO       |           | Level           | at reset                  |                                               |

| VDDIO    | 14,18     | PWR       | -               | -/-                       | Power supply for digital IOs (Typ.3.3V)       |

| VDD_REG  | 40        | PWR       | -               | _/_                       | Power supply for regulator input (Typ.3.3V)   |

| VDD_PA   | 29        | PWR       | -               | -/-                       | Power supply for PA block (Typ.3.3V)          |

| VDD_RF   | 32        | PWR       | -               | _/_                       | Power supply for LNA,MIX blocks (Typ.1.5V)    |

| VDD_IF   | 23        | PWR       | -               | -/-                       | Power supply for IF block (Typ.1.5V)          |

| VDD_VCO  | 39        | PWR       | -               | _/_                       | Power supply for VCO block (Typ.1.5V)         |

| VDD_CP   | 34        | PWR       | -               | -/-                       | Power supply for Charge Pump block (Typ.1.5V) |

| -        | EL        | GND       | -               | -/-                       | GND PAD                                       |

### •Unused pins

Followings are recommendation for unused pins

| Pin Name | Recommendation                         |

|----------|----------------------------------------|

| XOUT     | Fixed to GND (When TCXO is used)       |

| XIN      | Fixed to GND(When TCXO is used)        |

| TCXO     | Fixed to GND(When Cristal OSC is used) |

| ATEST1   | Left OPEN                              |

| ATEST2   | Left OPEN                              |

| A_MON    | Left OPEN                              |

| ANT_SW   | Left OPEN                              |

| DMON     | Left OPEN *1                           |

| DCNT     | Left OPEN                              |

\*1 If not using DMON, it is necessary to stop clock out (default output on DMON) by bit4 (CLKOUT\_EN) of register [CLK\_SET] address (B1 0x02). Left open with enableing clock out causes the performance down on RX sensitivity.

### ML7396A/B/E

# ■ELECTRICAL CHARACTERISTICS

### •Absolute maximum ratings

| Item                        | Symbol            | Condition      | Rating                         | Unit  |

|-----------------------------|-------------------|----------------|--------------------------------|-------|

| Power Supply (I/O) (*1)     | V <sub>DDIO</sub> |                | -0.3 to +4.6                   | V     |

| Power Supply (RF) (*2)      | V <sub>DDRF</sub> |                | -0.3 to +2.0                   | V     |

| Digital Input Voltage       | V <sub>DIN</sub>  |                | -0.3 to V <sub>DDIO</sub> +0.3 | V     |

| RF Input Voltage            | V <sub>RFIN</sub> |                | -1.0 to +2.0                   | V     |

| Analog Input Voltage        | V <sub>AIN</sub>  |                | -0.3 to V <sub>DDIO</sub> +0.3 | V     |

| Analog Input Voltage2 (*3)  | V <sub>AIN2</sub> |                | -0.3 to V <sub>DDRF</sub> +0.3 | V     |

| TCXO Input Voltage          | VTCXO             |                | -0.3 to +1.75                  | V     |

| Digital Output Voltage      | V <sub>DO</sub>   | Ta=-40 to 85°C | -0.3 to V <sub>DDIO</sub> +0.3 | V     |

| RF Output Voltage           | V <sub>RFO</sub>  | GND=0V         | -0.3 to V <sub>DDRF</sub> +1.9 | V     |

| Analog Output Voltage       | V <sub>AO</sub>   |                | -0.3 to V <sub>DDIO</sub> +0.3 | V     |

| Analog Output Voltage2 (*4) | V <sub>AO2</sub>  |                | -0.3 to V <sub>DDRF</sub> +0.3 | V     |

| Digital Input Current       | I <sub>DI</sub>   |                | -10 to +10                     | mA    |

| RF Input Current            | I <sub>RF</sub>   |                | -2 to +2                       | mA    |

| Analog Input Current        | I <sub>AI</sub>   |                | -2 to +2                       | mA    |

| Analog Input Current2 (*3)  | I <sub>AI2</sub>  |                | -2 to +2                       | mA    |

| TCXO Input Current          | Ітсхо             |                | -2 to +2                       | mA    |

| Digital Output Current      | I <sub>DO</sub>   |                | -8 to +8                       | mA    |

| RF Output Current           | I <sub>RFO</sub>  |                | -2 to +60                      | mA    |

| Analog Output Current       | I <sub>AO</sub>   | ]              | -2 to +2                       | mA    |

| Analog Output Current2 (*4) | I <sub>AO2</sub>  |                | -2 to +2                       | mA    |

| Power Dicipatin             | P <sub>d</sub>    | Ta=+25°C       | 300                            | mW    |

| Storage Temperature         | T <sub>stg</sub>  | _              | -55 to +150                    | deg.C |

\*1 VDD\_IO, VDD\_REG, VDD\_PA pins

\*2 VDD\_RF, VDD\_IF, VDD\_VCO, VDD\_CP pins

\*3 XIN, TCXO pins

\*4 XOUT pin

# LAPIS Semiconductor Co., Ltd.

### •Recommended operating conditions

| Item                                    | Symbol            | Conditions                                    | Min            | Тур | Max            | Unit  |

|-----------------------------------------|-------------------|-----------------------------------------------|----------------|-----|----------------|-------|

| Power Supply (I/O)                      | V <sub>DDIO</sub> | VDD_IO, VDD_REG pins                          | 1.8            | 3.3 | 3.6            | V     |

|                                         |                   | VDD_PA pin<br>TX power <= 1mW                 | 1.8            | 3.3 | 3.6            | V     |

| Power Supply (PA)                       | V <sub>DDPA</sub> | VDD_PA pin<br>TX power = 10mW                 | 2.3            | 3.3 | 3.6            | V     |

|                                         |                   | VDD_PA pin<br>TX power = 20mW                 | 2.6            | 3.3 | 3.6            | V     |

| Power Supply (RF) (*3)                  | V <sub>DDRF</sub> | VDD_RF,<br>VDD_IF,<br>VDD_VCO,<br>VDD_CP pins | 1.4            | 1.5 | 1.6            | V     |

| Ambient Temperature                     | Ta                | -                                             | -40            | +25 | +85            | deg.C |

| Rising time Digital Input               | T <sub>IR</sub>   | Digital input pins (*1)                       | -              | —   | 20             | Ns    |

| Falling time Digital Input              | T <sub>IF</sub>   | Digital Input pins (*1)                       | —              | _   | 20             | Ns    |

| Output loads Digital Ouput              | C <sub>DL</sub>   | All Digital Output pins                       | —              | —   | 20             | pF    |

| 36MHz Xtal frequency<br>(Master Clock1) | F <sub>MCK1</sub> | XIN, XOUT pins                                | -20ppm<br>(*3) | 36  | +20ppm<br>(*3) | MHz   |

| 36MHz TCXO frequency<br>(Master Clock2) | F <sub>MCK2</sub> | TCXO pin                                      | -20ppm<br>(*3) | 36  | +20ppm<br>(*3) | MHz   |

| TCXO Input                              | V <sub>TCXO</sub> | DC cut                                        | 0.8            | -   | 1.5            | Vpp   |

| SPI clock frequency                     | F <sub>SCLK</sub> | SCLK pin                                      | 0.032          | 2   | 16             | MHz   |

| SPI clock duty ratio                    | D <sub>SCLK</sub> | SCLK pin                                      | 45             | 50  | 55             | %     |

| RF channel frequency                    | F <sub>RF</sub>   | LNA_P,PA_OUT pins                             | 863            | -   | 960            | MHz   |

\*1 Those pins with symbol I, Is at pin definition section

\*2 Use REG\_OUT output of this LSI.

\*3 It's max.+10ppm and min.-10ppm at 10kbps setting.

### [Note]

Electrical characteristics are in the above recommended operating conditions without special instruction.

\* Following "Typ" value is not guaranteed value studied variation of IC but typical centre value.

### •Power consumption

| Item                   | Symbol | Conditions                                | Min | Typ (*2) | Max     | Unit |

|------------------------|--------|-------------------------------------------|-----|----------|---------|------|

| Power Consumption (*1) | IDD1   | Sleep state<br>(Maintain register values) | I   | 0.9      | 3.0(*3) | μΑ   |

|                        | IDD2   | Idle state                                | -   | 1.4      | 3.0     | mA   |

|                        | IDD3   | RF RX state (*4)                          | _   | 15.0     | 20.0    | mA   |

|                        | IDD4   | RF TX state (1mW) (*4)                    | 1   | 13.0     | 20.0    | mA   |

|                        | IDD5   | RF TX state (10mW) (*4)                   | _   | 24.0     | 35.0    | mA   |

|                        | IDD6   | RF TX state (20mW) (*4)                   | _   | 32.0     | 43.0    | mA   |

\*1 Power consumption is sum of current consumption of all power supply pins

\*2 "Typ" value is centre value under condition of VDDIO=3.3V, 25deg.C.

\*3 "Typ", "Max" values are under condition of 25deg.C

\*4 Current value when the data rate is 100kbps and the frequency is 920MHz.

### •DC characteristics

| Item                         | Symbol   | Conditions                            | Min                        | Typ (*2) | Max                        | Unit |

|------------------------------|----------|---------------------------------------|----------------------------|----------|----------------------------|------|

| Voltage Input High           | VIH1     | Digital input/inout pins              | V <sub>DDIO</sub><br>x0.75 | _        | V <sub>DDIO</sub>          | V    |

| vonage input righ            | VIH2     | XIN pin                               | V <sub>DDRF</sub><br>x0.9  | -        | V <sub>DDRF</sub>          | v    |

| Voltage Input Low            | VIL1     | Digital input/inout pins              | 0                          | _        | V <sub>DDIO</sub><br>x0.18 | V    |

| vonage input Low             | VIL2     | XIN pin                               | 0                          | _        | V <sub>DDRF</sub><br>X0.1  | v    |

| Threshold Voltage High level | VT+      | Digital pins with shmitt trigger gate | _                          | 1.2      | V <sub>DDIO</sub><br>x0.75 | V    |

| Threshold Voltage Low level  | VT-      | Digital pins with shmitt trigger gate | V <sub>DDIO</sub><br>x0.18 | 0.8      | _                          | V    |

|                              | IIH1     | Digital input pins                    | -1                         | _        | 1                          | ìA   |

| Input Leakage Current        | IIH2     | XIN pin                               | -0.3                       | _        | 0.3                        | ìA   |

| input Loundge Curront        | IIL1     | Digital input pins                    | -1                         | _        | 1                          | ìA   |

|                              | IIL2     | XIN pin                               | -0.3                       | _        | 0.3                        | ìA   |

| Output Leakage               | IOZH1    | Digital inout pins                    | -1                         | _        | 1                          | ìA   |

| Current 3-state pins         | IOZL1    | Digital inout pins                    | -1                         | _        | 1                          | ìA   |

| Voltage Ouput level H        | VOH      | IOH=-4mA /-2mA (*1)                   | V <sub>DDIO</sub><br>x0.8  | _        | V <sub>DDIO</sub>          | V    |

| Voltage Ouput level L        | VOL      | IOL=4mA /2mA (*1)                     | 0                          | _        | 0.3                        | V    |

| Regulator output             | REG_CORE | Sleep state                           | 0.95                       | 1.3      | 1.65                       | v    |

| voltage                      | (*2)     | Other states                          | 1.40                       | 1.5      | 1.60                       | v    |

|                              | CIN      | Input pins                            | _                          | 6        | _                          | pF   |

| Din Conscitones              | COUT     | Output pins                           | _                          | 9        | _                          | pF   |

| Pin Capacitance              | CRFIO    | RF inout pins                         | -                          | 9        | _                          | pF   |

|                              | CAI      | Analog input pins                     | -                          | 9        | _                          | pF   |

\_\_\_\_\_

\*1 DMON pin\*2 REG\_CORE pin and REG\_OUT pin

## LAPIS Semiconductor Co., Ltd.

### •RF characteristics

| Data Rate         | : | 10kbps/ 20kbps/ 40kbps/ 50kbps/100kbps/ 150kbps/200kbps/ 400kbps             |

|-------------------|---|------------------------------------------------------------------------------|

| Modulation scheme | : | GFSK                                                                         |

| Channel spacing   | : | 200kHz/400kHz/600kHz                                                         |

| Frequency         | : | Support 750MHz to 1GHz by changing L/C components between IND1 and IND2 pins |

[TX]

| Item                                            | Condition                                                                                                                                                                                                                                                | Min   | Тур | Max     | Unit |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|---------|------|

| TX Power                                        | 20mW(13dBm) mode                                                                                                                                                                                                                                         | 9     | 13  | 15      | dBm  |

| IXFOWE                                          | 10mW(10dBm) mode                                                                                                                                                                                                                                         | 6     | 10  | 12      | dBm  |

|                                                 | 1mW(0dBm) mode                                                                                                                                                                                                                                           | -4    | 0   | 2       | dBm  |

| Adjustment range of frequency shift [Fdev] (*1) |                                                                                                                                                                                                                                                          | _     |     | 2,250   | kHz  |

| 920MHz band (920.5MHz to 928.                   |                                                                                                                                                                                                                                                          |       |     |         |      |

| Occupied bandwidth                              | n : number of channel                                                                                                                                                                                                                                    | _     |     | 200 x n | kHz  |

| Power at edge of channel                        | 20mW mode (920.5MHz to 922.3MHz)                                                                                                                                                                                                                         | _     | _   | -7      | dBm  |

| Tower at edge of channel                        | 10mW mode                                                                                                                                                                                                                                                | _     | -   | -10     | dBm  |

|                                                 | 1mW mode                                                                                                                                                                                                                                                 | _     | _   | -20     | dBm  |

| A dia cont Channel Desson                       | 20mW mode ±1CH, bandwidth 200kHz)                                                                                                                                                                                                                        | _     | -33 | -15     | dBm  |

| Adjacent Channel Power                          | 10mW mode +/-1ch bandwidth: 200kHz                                                                                                                                                                                                                       | _     | -39 | -18     | dBm  |

|                                                 | 1mW mode +/-1ch bandwidth: 200kHz                                                                                                                                                                                                                        | _     | -47 | -26     | dBm  |

| Modulation index accuracy                       | In IEEE802.15.4g opetation                                                                                                                                                                                                                               | -20   |     | +20     | %    |

| Unnecessary emission level                      | 710MHz or lower, 100kHz band                                                                                                                                                                                                                             | _     | -65 | -36     | dBm  |

| (20mW mode)                                     | Higher than 710MHz to 900MHz, 1MHz band                                                                                                                                                                                                                  | _     | -70 | -55     | dBm  |

|                                                 | Higher than 900MHz to 915MHz, 100kHz band                                                                                                                                                                                                                | _     | -72 | -55     | dBm  |

|                                                 | Higher than 915MHz to 930MHz, 100kHz band<br>(Excluding within 200 + 100xnkHz above and<br>below the channel frequency, however, within<br>100 + 100xnkHz above and below for<br>920.5MHz to 922.3MHz. n is the number of<br>concurrently used channels) | _     | -51 | -36     | dBm  |

|                                                 | Higher than 930MHz to 1000MHz, 100kHz band                                                                                                                                                                                                               | _     | -70 | -55     | dBm  |

|                                                 | Higher than 1000MHz to 1215MHz, 1MHz band                                                                                                                                                                                                                | _     | -75 | -45     | dBm  |

|                                                 | Higher than 1215MHz, 1MHz band<br>(2nd harmonics or higher)                                                                                                                                                                                              | —     | -40 | -30     | dBm  |

|                                                 | 710MHz or lower, 100kHz band                                                                                                                                                                                                                             | _     | -65 | -36     | dBm  |

|                                                 | Higher than 710MHz to 900MHz, 1MHz band                                                                                                                                                                                                                  | _     | -70 | -55     | dBm  |

| RF Frequency                                    | LNA P,PA OUT                                                                                                                                                                                                                                             | 750.0 | _   | 1000.0  | MHz  |

| 915MHz band (902MHz to 928M                     | Hz)                                                                                                                                                                                                                                                      |       |     |         |      |

| 6dB bandwidth                                   | Frequency shift=171kHz                                                                                                                                                                                                                                   | 500   | —   | _       | kHz  |

| Power spectrum density                          | 20mW mode, frequency shift = 171kHz, 3kHz<br>band                                                                                                                                                                                                        | _     | _   | 8       | dBm  |

| Unnecessary emission level                      | 900MHz or lowe                                                                                                                                                                                                                                           | _     | -65 | -56     | dBm  |

| (20mW mode)                                     | Higher than 960MHz (2nd harmonics or higher)                                                                                                                                                                                                             | _     | -50 | -41     | dBm  |

| 868MHz band (863MHz to 870M                     | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                  |       |     | 1       |      |

| Unnecessary emission level<br>(10mW mode)       | Higher than 1000MHz (2nd harmonics or higher)                                                                                                                                                                                                            | _     | -35 | -30     | dBm  |

\*1 While the adjustment range is described as above, the possible maximum value depends on the RF channel frequency to be used.

RF channel frequency  $\pm$  frequency shift should not include a multiple of 36MHz (864MHz, 900MHz, 936MHz, and so on).

Example) For 902MHz, 2,000kHz can be set at a maximum.

\*2 863.5MHz to 866.2MHz cannot be used. For details, see section "Setting channel frequency."

### [RX]

| Item                                     | Condition                                                     | Min | Тур   | Max  | Unit |

|------------------------------------------|---------------------------------------------------------------|-----|-------|------|------|

| 920MHz band (920.5MHz to 928             | 3.1MHz)                                                       |     |       |      | •    |

| Mining DY and it it                      | 50kbps mode (NBO_SEL=0)                                       | _   | -107  | -102 | dBm  |

| Minimum RX sensitivity<br>BER<0.1%       | 100kbps mode (NBO_SEL=0)                                      | —   | -105  | -100 | dBm  |

| BER~0.170                                | 200kbps mode (NBO_SEL=0)                                      | —   | -102  | -97  | dBm  |

| Maximum input level                      | 50kbps mode/100kbps mode/200kbps mode                         | 0   | —     | -    | dBm  |

|                                          | 50kbps mode                                                   | 20  | 35    | —    | dB   |

| RX C/I Adjacent Channel                  | 100kbps mode                                                  | 20  | 35    | —    | dB   |

|                                          | 200kbps mode                                                  | 20  | 35    | _    | dB   |

|                                          | 50kbps mode                                                   | 30  | 45    | _    | dB   |

| RX C/I second adjacent interference      | 100kbps mode                                                  | 30  | 45    | _    | dB   |

| Interference                             | 200kbps mode                                                  | 30  | 45    | -    | dB   |

| Minimum power detection level            |                                                               | _   | _     | -100 | dBm  |

| Power detection range                    |                                                               | 60  | 70    | —    | dB   |

| Power detection accuracy                 |                                                               | -6  | —     | +6   | dB   |

|                                          | Compliant with FCC, ARIB, ETSI standard                       | _   | _     | TBD  | dBm  |

|                                          |                                                               | _   | —     | TBD  | dBm  |

| Spurious Emission level                  |                                                               | _   | _     | TBD  | dBm  |

| ARIB T108 measurement                    |                                                               | _   | _     | TBD  | dBm  |

| condition                                |                                                               | _   | _     | TBD  | dBm  |

| 915.9MHz~916.9MHz                        |                                                               | _   | _     | TBD  | dBm  |

| 920.5MHz~929.7MHz                        |                                                               | _   | _     | TBD  | dBm  |

|                                          |                                                               | _   | _     | TBD  | dBm  |

|                                          |                                                               | _   | _     | TBD  | dBm  |

| 915MHz band (902MHz to 928M              | (Hz)                                                          |     |       |      |      |

| , ,                                      | 100kbps mode (when NBO_SEL is 0, the modulation index is 1)   | _   | -105  | -99  | dBm  |

|                                          | 150kbps mode (when NBO_SEL is 0, the modulation index is 0.5) | _   | -102  | -96  | dBm  |

| Minimum receiver sensitivity<br>BER<0.1% | 200kbps mode (when NBO_SEL is 0, the modulation index is 1)   | _   | -102  | -96  | dBm  |

|                                          | 100kbps mode (frequency shift: 171kHz)                        | _   | -100  | -87  | dBm  |

|                                          | 150kbps mode (frequency shift: 171kHz)                        | _   | -97.5 | -84  | dBm  |

|                                          | 200kbps mode (frequency shift: 171kHz)                        | _   | -96.5 | -83  | dBm  |

| 868MHz band (863MHz to 870M              | (Hz) (*1)                                                     |     | •     |      |      |

|                                          | 50kbps mode (when NBO_SEL is 0)                               | —   | -107  | -102 | dBm  |

| Minimum receiver sensitivity BER<0.1%    | 100kbps mode (when NBO_SEL is 0)                              | _   | -105  | -100 | dBm  |

| DER~0.170                                | 200kbps mode (when NBO_SEL is 0)                              | _   | -102  | -97  | dBm  |

| Collectorel environments of the st       | 1000MHz or lower (local frequency)                            | _   | -63   | -57  | dBm  |

| Collateral emission level                | Higher than 1000MHz                                           | _   | -57   | -47  | dBm  |

\*1 863.5MHz to 866.2MHz cannot be used. For details, see section "Setting channel frequency."

### ML7396A/B/E

#### ML7396A/B/E

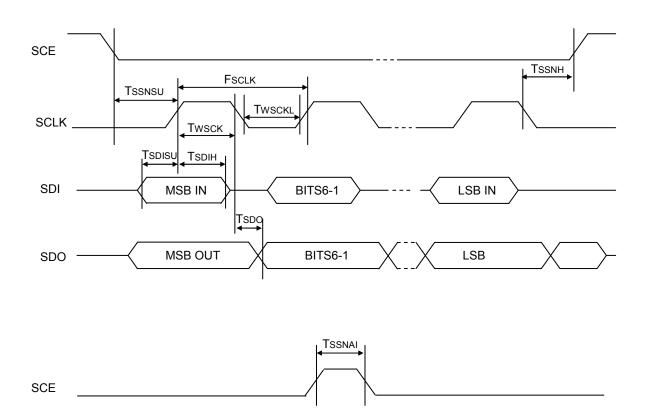

### •SPI interface

| Item                   | Symbol | Condition                   | Min   | Тур | Max | Unit |

|------------------------|--------|-----------------------------|-------|-----|-----|------|

| SCLK clock frequency   | FSCLK  |                             | 0.032 | 2   | 16  | MHz  |

| SCEN input setup time  | TSSNSU |                             | 30    | -   | -   | ns   |

| SCEN input hold time   | TSSNH  |                             | 30    | _   | _   | ns   |

| SCLK high pulse width  | Twsckh | <b>.</b>                    | 28    | _   | _   | ns   |

| SCLK low pulse width   | TWSCKL | Load capacitance<br>CL=20pF | 28    | _   | _   | ns   |

| SDI input setup time   | Tsdisu | CL-20pi                     | 5     | _   | _   | ns   |

| SDI input hold time    | Tsdih  |                             | 15    | -   | _   | ns   |

| SCEN Negation interval | TSSNAI |                             | 60    | -   | -   | ns   |

| SDO output delay       | Tsdo   |                             | -     | -   | 22  | ns   |

[Note]

All timing parameter is defined at voltage level of  $V_{\text{DDIO}}\,x$  20% and  $V_{\text{DDIO}}.$

### ML7396A/B/E

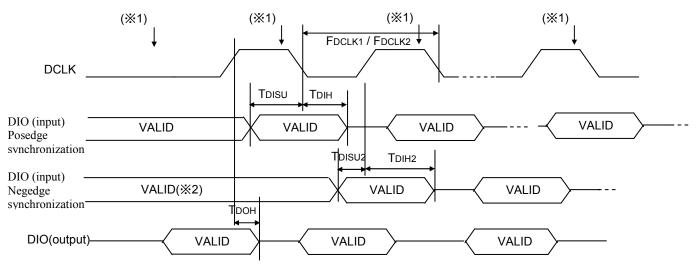

### •DIO interface

| Item                                                          | Symbol             | Condition                   | Min            | Тур              | Max    | Unit |

|---------------------------------------------------------------|--------------------|-----------------------------|----------------|------------------|--------|------|

| DIO input setup time<br>(DCLK Posedge<br>synchronization)     | Tdisu              |                             | 1              | _                | _      | us   |

| DIO input setup time<br>(DCLK Negedge<br>synchronization)     | TDISU2             |                             | 0              | _                | _      | us   |

| DIO input hold time<br>(DCLK Posedge<br>synchronization)      | Tdih               |                             | 0              |                  | _      | ns   |

| DIO input hold time (*3)<br>(DCLK Negedge<br>synchronization) | Tdih2              |                             | 10<br>5<br>2.5 | _                | _      | us   |

| DIO Output hold time                                          | T <sub>DOH</sub>   | Load capacitance<br>CL=20pF | 20             | -                | —      | ns   |

| DCLK clock frequency<br>(*1) (*3)<br>(TX)                     | F <sub>DCLK1</sub> |                             | -20ppm         | 50<br>100<br>200 | +20ppm | kHz  |

| DCLK clock frequency<br>(*2) (*3)<br>(RX)                     | F <sub>DCLK2</sub> |                             | -4%            | 50<br>100<br>200 | +4%    | kHz  |

| DCLK clock output duty<br>ratio (TX)                          | D <sub>DCLK</sub>  |                             | _              | 50               | _      | %    |

| DCLK clock output duty ratio (RX)                             | D <sub>DCLK</sub>  |                             | 40             | _                | 60     | %    |

\*1 DCLK clock frequency in TX mode will be varied depending on the variance of master clock frequency.

\*2 DCLK clock frequency in RX mode will be varied by reproduced clock and its jitter.

\*3 These characteristics are depend on data rate value of bit2-0(RATE [2:0]) of register [DATA\_SET]. (upper: 50kbps, mid: 100kbps, lower: 200kbps)

#### [Note]

All timing parameter is defined at voltage level of  $V_{DDIO} \ge 20\%$  and  $V_{DDIO}$ .

(\*1) Timing when this LSI takes the DIO input.

(\*2) For the Negedge synchronization, the first two bits of data to be input from DIO have the same data.

ML7396A/B/E

### •Clock output

Register [CLK\_SET] address (B0 0x02) sets if clock output enable or not(Initial value:enable), freaquency output to DMON pin.

| Item                    | Symbol              | Co                             | ndition          | Min    | Тур | Max | Unit |

|-------------------------|---------------------|--------------------------------|------------------|--------|-----|-----|------|

| Clock output frequency  | F <sub>CLKOUT</sub> |                                |                  | 0.0088 | 6   | 36  | MHz  |

| Clock output duty ratio | D                   | Load<br>capacitance<br>CL=20pF | 12MHz            | 30     | -   | 70  | %    |

| (*1)                    | D <sub>CLKOUT</sub> | CL 20pr                        | Other than above | 48     | 50  | 52  | %    |

\*1 Duty ratio will be H:L = 1:2 when output frequency is 12MHz.. See register [CLK\_OUT] address (B0 0x03).

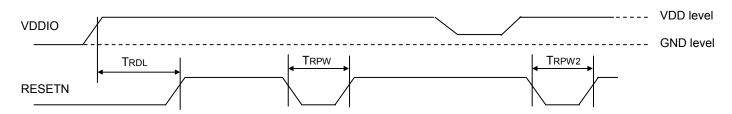

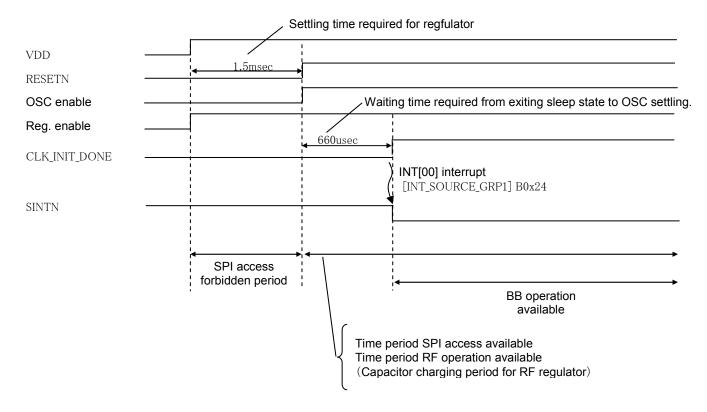

#### •Reset

| Item                                                              | Symbol           | Condition                                 | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|------------------|-------------------------------------------|-----|-----|-----|------|

| RESETN delay time (Power on)                                      | T <sub>RDL</sub> | All power supply pins<br>(After power on) | 1.5 | _   | _   | ms   |

| RESETN assert time (pulse width)<br>(When starting from VDDIO=0V) | T <sub>RPW</sub> |                                           | 200 | _   | _   | ns   |

| RESETN pulse time 2 (*1)<br>(When starting from VDDIO≠0V)         | Trpw2            | VDD>1.8V                                  | 1.5 | _   | _   | ms   |

(\*1) When starting from VDDIO≠.0V, input a pulse to the RESETN signal after VDDIO exceeds 1.8V.

### ML7396A/B/E

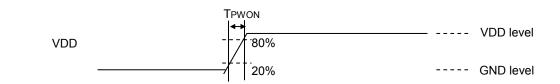

### •Power on sequence

| Item                         | Symbol            | Condition                                 | Min | Тур | Max | Unit |

|------------------------------|-------------------|-------------------------------------------|-----|-----|-----|------|

| Power on time<br>differences | T <sub>PWON</sub> | Power on state<br>(All power supply pins) | -   | -   | 5   | ms   |

ML7396A/B/E

# REGISTERS

#### •Register map

It is consist of 3bank, BANK0, BANK1, BANK2. Each BANK has address space of 0x00 to 0x7F 128 byte in total. The space shown as gray highlighted part is not implemented in LSI or reserved bits. TX/RX FIFO is implemented in PHY block, those register except for FIFO is implemented in SPI block. The address not exisit in the memory map is not accesible. Also, the address is not accessible during the VCO calibration.

For registers whose setting value is specifically shown in the register list, please set the value shown in the list and do not change it.

: Implemented as functionable register

: Impelemted as reserved bits

# LAPIS Semiconductor Co., Ltd.

### BANK0

| AddressSymbol<br>(# test register)0x00BANK_SEL0x01RST_SET0x02CLK_SET0x03CLKOUT0x04RATE_SET10x05RATE_SET20x06-0x07Reserved0x08#ADC_CLK_SET0x09-0x0aReserved0x0b#OSC_ADJ0x0c#RF_TEST_MODE0x0d-0x0eReserved0x0f# PHY_STATE0x10#FIFO BANK                                                                           | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Description<br>Register access destination (BANK) select<br>Software reset control<br>Clock configuration                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|---|---|---|---|---|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01RST_SET0x02CLK_SET0x03CLKOUT0x04RATE_SET10x05RATE_SET20x06-0x07Reserved0x08#ADC_CLK_SET0x09-0x0aReserved0x0b#OSC_ADJ0x0c#RF_TEST_MODE0x0d-0x0eReserved0x0f# PHY_STATE                                                                                                                                       |          |   |   |   |   |   |   |   | Software reset control                                                                                                                                  |

| 0x02CLK_SET0x03CLKOUT0x04RATE_SET10x05RATE_SET20x06-0x07Reserved0x08#ADC_CLK_SET0x09-0x0aReserved0x0b#OSC_ADJ0x0c#RF_TEST_MODE0x0d-0x0eReserved0x0f# PHY_STATE                                                                                                                                                  |          |   |   |   |   |   |   |   |                                                                                                                                                         |

| 0x03         CLKOUT           0x04         RATE_SET1           0x05         RATE_SET2           0x06-0x07         Reserved           0x08         #ADC_CLK_SET           0x09-0x0a         Reserved           0x0b         #OSC_ADJ           0x0c         #RF_TEST_MODE           0x0d-0x0e         Reserved   |          |   |   |   |   |   |   |   | Clock configuration                                                                                                                                     |

| 0x04         RATE_SET1           0x05         RATE_SET2           0x06-0x07         Reserved           0x08         #ADC_CLK_SET           0x09-0x0a         Reserved           0x0b         #OSC_ADJ           0x0c         #RF_TEST_MODE           0x0d-0x0e         Reserved           0x0d         Reserved |          |   |   |   |   |   |   |   |                                                                                                                                                         |

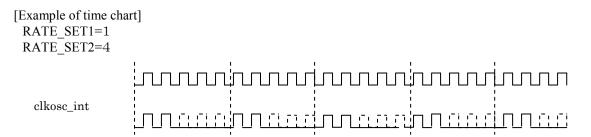

| 0x05RATE_SET20x06-0x07Reserved0x08#ADC_CLK_SET0x09-0x0aReserved0x0b#OSC_ADJ0x0c#RF_TEST_MODE0x0d-0x0eReserved0x0f# PHY_STATE                                                                                                                                                                                    |          |   |   |   |   |   |   |   | Frequency setting of CLKOUT output                                                                                                                      |

| 0x06-0x07Reserved0x08#ADC_CLK_SET0x09-0x0aReserved0x0b#OSC_ADJ0x0c#RF_TEST_MODE0x0d-0x0eReserved0x0f# PHY_STATE                                                                                                                                                                                                 |          |   |   |   |   |   |   |   | Data rate conversion setting 1                                                                                                                          |

| 0x08#ADC_CLK_SET0x09-0x0aReserved0x0b#OSC_ADJ0x0c#RF_TEST_MODE0x0d-0x0eReserved0x0f# PHY_STATE                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | Data rate conversion setting 2                                                                                                                          |

| 0x09-0x0aReserved0x0b#OSC_ADJ0x0c#RF_TEST_MODE0x0d-0x0eReserved0x0f# PHY_STATE                                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | Reserved                                                                                                                                                |

| 0x0b#OSC_ADJ0x0c#RF_TEST_MODE0x0d-0x0eReserved0x0f# PHY_STATE                                                                                                                                                                                                                                                   |          |   |   |   |   |   |   |   | ADC clock setting for RSSI                                                                                                                              |

| 0x0c#RF_TEST_MODE0x0d-0x0eReserved0x0f# PHY_STATE                                                                                                                                                                                                                                                               |          |   |   |   |   |   |   |   | Reserved                                                                                                                                                |

| 0x0d-0x0e         Reserved           0x0f         # PHY_STATE                                                                                                                                                                                                                                                   |          |   |   |   |   |   |   |   | Load capacitor trimming in oscillation circuit                                                                                                          |

| 0x0f # PHY_STATE                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | RF TX test pattern configuration                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                 |          |   |   |   |   |   |   |   | Reserved                                                                                                                                                |

| 0x10 #FIEO BANK                                                                                                                                                                                                                                                                                                 |          |   |   |   |   |   |   |   | PHY state display                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                 |          |   |   |   |   |   |   |   | FIFO bank display                                                                                                                                       |

| 0x11 #PLL LOCK DETECT                                                                                                                                                                                                                                                                                           |          |   |   |   |   |   |   |   | Parameter setting for PLL lock detection                                                                                                                |

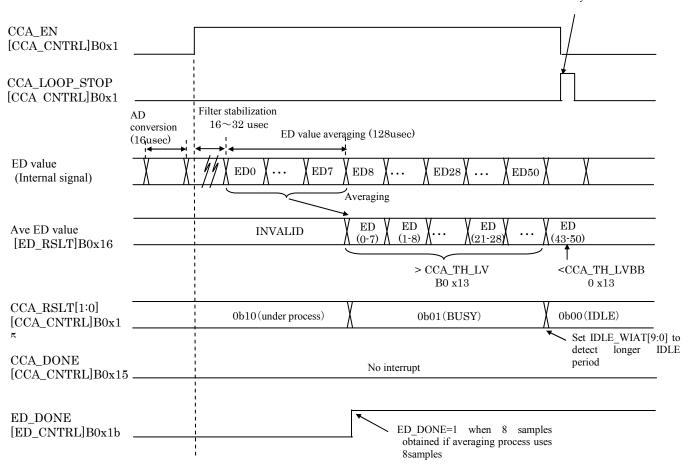

| 0x12 CCA_IGNORE_LEVEL                                                                                                                                                                                                                                                                                           |          |   |   |   |   |   |   |   | ED threshold level to exclude CCA judgement                                                                                                             |

| 0x13 CCA_LEVEL                                                                                                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | Threshold level for CCA operation                                                                                                                       |

| 0x14 CCA ABORT                                                                                                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | Time parameter to terminate CCA operation during AUTO_ACK case                                                                                          |

| 0x15 CCA CNTRL                                                                                                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | CCA control setting and reporting result                                                                                                                |

| 0x16 ED RSLT                                                                                                                                                                                                                                                                                                    |          |   |   |   |   |   |   |   | Readout register for ED (Energy Detection) values                                                                                                       |

| 0x17 IDLE WAIT L                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | Time parameter to judge as IDLE state during CCA operation. (lower 8bits)                                                                               |

| 0x18 IDLE WAIT H                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | Time parameter to judge as IDLE state during CCA operation (upper 2bits)                                                                                |

| 0x19 CCA PROG L                                                                                                                                                                                                                                                                                                 |          |   | - |   |   |   |   |   | Elapsed time as IDLE state during CCA operation (lower 8bits)                                                                                           |

| 0x1a CCA PROG H                                                                                                                                                                                                                                                                                                 |          |   |   |   |   |   |   |   | Elapsed time as IDLE state during CCA operation (upper 2bits)                                                                                           |

| 0x1b ED CNTRL                                                                                                                                                                                                                                                                                                   |          |   |   |   |   |   |   |   | ED (Energy Detection) control                                                                                                                           |

| Ox1c GAIN MtoL                                                                                                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | Threshold level to switch from middle gain to low gain                                                                                                  |

| 0x1d GAIN LtoM                                                                                                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | Threshold level to switch from low gain to middle gain                                                                                                  |

| 0x1e GAIN HtoM                                                                                                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | Gain update setting and threshold level to switch from high gain to middle gain                                                                         |

| 0x1f GAIN MtoH                                                                                                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | Threshold level to switch from middle gain to high gain                                                                                                 |

| 0x20 RSSI_ADJ_M                                                                                                                                                                                                                                                                                                 |          |   |   |   |   |   |   |   | RSSI offset value in middle gain range                                                                                                                  |

| 0x21 RSSI ADJ L                                                                                                                                                                                                                                                                                                 |          |   |   |   |   |   |   |   | RSSI offset value in low gain range                                                                                                                     |

| 0x22 RSSI STABLE TIME                                                                                                                                                                                                                                                                                           |          |   |   |   |   |   |   |   | Time parameter for RSSI value become stable after gain switch                                                                                           |

| 0x23 RSSI VAL ADJ                                                                                                                                                                                                                                                                                               |          |   |   |   |   |   |   |   | RSSI scale factor for ED value conversion.                                                                                                              |

| 0x24 INT SOURCE GRP1                                                                                                                                                                                                                                                                                            |          |   |   |   |   |   |   |   | FIFO clear setting, interrupt status for INT05 to INT00                                                                                                 |

| 0x25 INT SOURCE GRP2                                                                                                                                                                                                                                                                                            |          |   |   |   |   |   |   |   | Interrupt status for INT15 to INT8                                                                                                                      |

| 0x26 INT SOURCE GRP3                                                                                                                                                                                                                                                                                            |          |   |   |   |   |   |   |   | Interrupt status for INT23 to INT16                                                                                                                     |

| 0x27 INT SOURCE GRP4                                                                                                                                                                                                                                                                                            |          |   |   |   |   |   |   |   | Interrupt status for INT25 to INT24                                                                                                                     |

| 0x28 PD DATA REQ                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | Data transmission request                                                                                                                               |

| 0x29 PD DATA IND                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | Data reception reporting                                                                                                                                |

| 0x2a INT EN GRP1                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | Interrupt mask for INT03 to INT00                                                                                                                       |

| 0x2b INT EN GRP2                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | Interrupt mask for INT15 to INT08                                                                                                                       |

| 0x2c INT EN GRP3                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | Interrupt mask for INT23 to INT16                                                                                                                       |

| 0x2d INT EN GRP4                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | Interrupt mask for INT25 and INT24                                                                                                                      |

| 0x2e CH EN L                                                                                                                                                                                                                                                                                                    | ┝─┤      |   |   |   |   |   |   |   | Channel enable setting for lower 8ch                                                                                                                    |

| 0x2f CH EN H                                                                                                                                                                                                                                                                                                    |          |   |   |   |   |   |   |   | Channel enable setting for upper 8ch                                                                                                                    |

| 0x30 IF FREQ AFC H                                                                                                                                                                                                                                                                                              | $\vdash$ |   |   |   |   |   |   |   | IF frequency setting in AFC mode. (upper 8bits)                                                                                                         |

| 0x31 IF FREQ AFC L                                                                                                                                                                                                                                                                                              |          |   |   |   |   |   |   |   | IF frequency setting in AFC mode (lower 8bits)                                                                                                          |

| 0x32 BPF AFC ADJ H                                                                                                                                                                                                                                                                                              |          |   |   |   |   |   |   |   | Capacitor trimming of band pass filter in AFC mode operation (upper 2bits)                                                                              |

| 0x33 BPF AFC ADJ L                                                                                                                                                                                                                                                                                              |          |   |   |   |   |   |   |   | Capacitor trimming of band pass filter in AFC mode operation (apper 2016)<br>Capacitor trimming of band pass filter in AFC mode operation (lower 8bits) |

| 0x34 AFC CNTRL                                                                                                                                                                                                                                                                                                  |          |   |   |   |   |   |   |   | AFC mode configuration                                                                                                                                  |

| 0x35 TX ALARM LH                                                                                                                                                                                                                                                                                                |          |   |   |   |   |   |   |   | Alert level setting for remaining size of TX FIFO (alarm for FIFO full)                                                                                 |

| 0x36 TX ALARM HL                                                                                                                                                                                                                                                                                                | $\vdash$ |   |   |   |   |   |   |   | Alert level setting for remaining size of TX FIFO (alarm for TX empty)                                                                                  |

| 0x30 IX_ALARM_IIL<br>0x37 RX ALARM LH                                                                                                                                                                                                                                                                           |          |   |   |   |   |   |   |   | Alert level setting for remaining size of RX FIFO (alarm for RX full)                                                                                   |

### BANK0 (continued)

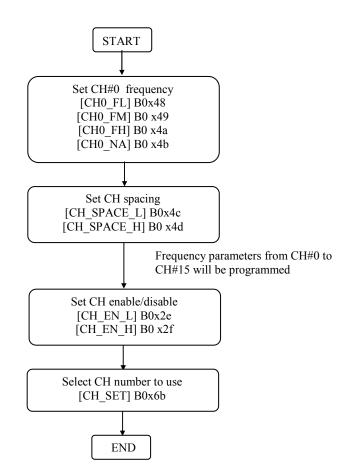

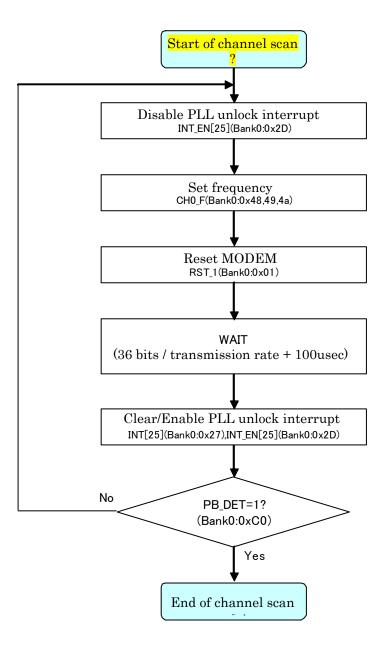

| Address      | Symbol<br>(# test register) | 7        | 6        | 5 | В<br>4   | it<br>3  | 2        | 1        | 0        | Description                                                                                                                                                      |