7.2.4. Модуль ICSv3

(Руководство разработчика по микроконтроллерам семейства HCS08)Модуль тактирования ICS третьей версии в составе МК серии QE имеет некоторые усовершенствования по сравнению с рассмотренными выше алгоритмами работы модуля тактирования:

- Расширен диапазон работы управляемого цифровым кодом генератора DCO. Теперь он может работать в трех диапазонах частот: от 16 до 20МГц, от 32 до 40МГц и от 48 до 60МГц. Выбор диапазона осуществляется битовым полем DRS в регистре ICSSC. Обратите внимание, что изменение битов DRS можно производить, только если FLL работает в активном режиме (LP = 0). Смена битов, произведенная во время работы FLL в режиме низкого потребления (LP = 1), не будет иметь эффекта.

- Расширен диапазон коэффициентов предварительного делителя частоты RDIV (см. Табл.7.5).

Таблица7.5. Коэффициент деления RDIV

| RDIV | RANGE = 0 | RANGE = 1 |

|---|---|---|

| 0 | 1 | 32 |

| 1 | 2 | 64 |

| 2 | 4 | 129 |

| 3 | 8 | 256 |

| 4 | 16 | 512 |

| 5 | 32 | 1024 |

| 6 | 64 | Резерв |

| 7 | 128 | Резерв |

- Введены новые программируемые коэффициенты умножения FLL, которые позволяют генерировать высокую частоту на выходе FLL при низкой опорной частоте, т.е. от «часового» кварцевого резонатора 32.768кГц. Опция для работы от «часового» кварцевого резонатора выбирается битом DMX32 в регистре ICSSC (см. Табл.7.6).

Таблица7.6. Режимы работы FLL при тактировании от «часового» кварцевого резонатора

| DRS | DMX32 | Опорная частота | Коэффициент умножения | Частота DCO |

|---|---|---|---|---|

| 00 | 0 | 31.25...39.0625кГц | 512 | 16...20МГц |

| 1 | 32.768кГц | 608 | 19.92МГц | |

| 01 | 0 | 31.25...39.0625кГц | 1024 | 32...40МГц |

| 1 | 32.768кГц | 1216 | 39.85МГц | |

| 10 | 0 | 31.25...39.0625кГц | 1536 | 48...60МГц |

| 1 | 32.768кГц | 1824 | 59.77МГц | |

| 11 | Резерв | |||

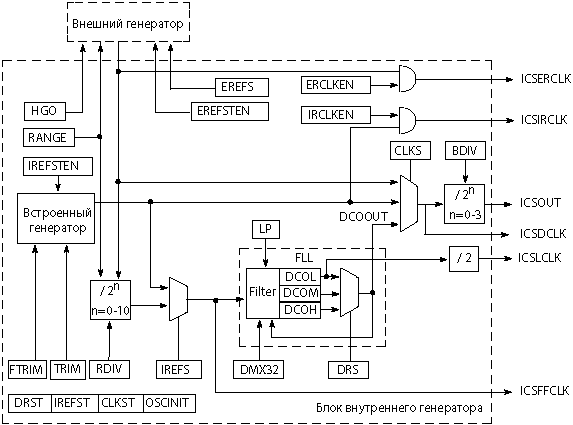

На Рис.7.10 представлена функциональная схема модуля ICSv3.

Рис.7.10. Функциональная схема модуля ICSv3.

Пример 7.3 показывает, как настроить модуль ICSv3 на работу в режиме FEI с частотой DCO, равной 48МГц, что соответствует частоте внутренней шины 24МГц. В главе 8 (Пример 8.4) также показано, как сконфигурировать модуль на работу в режимах FEI и FBE.

Пример 7.3. Инициализация модуля ICSv3 в режим FEI

#include

#include"derivative.h"/*includeperipheraldeclarations*/

#include"hcs08.h"/*Этонашфайлсобъявлениями!*/

#defineLED1BIT_0//PTC0

#defineLED2BIT_1//PTC1

//Простаяпрограммнаязадержка

voiddelay(unsignedintvalue)

{

for(;value;value--);

}

voidmain(void)

{

SOPT1=bBKGDPE;//ВрегистреSOPT1разрешаемфункциюдлявыводаBKGDдляотладки

ICSSC=DCO_HIGH|NVFTRIM;/*ПереписатьзначениебитаFTRIM,выбратьдляDCO

верхнийдиапазонработы*/

ICSTRM=NVICSTRM;//ПереписатьподстроечноечислоTRIM

ICSC1=ICS_FLL|bIREFS;//ВыбратьрежимFEI(ICSOUT=DCOOUT=1536*IRCLK)

ICSC2=BDIV_1;//ICSOUT=DCOOUT/1

PTCDD=0xFF;//ЛинииPTC–навывод

PTCD=0xFE;//LED1включен,LED2выключен

while(1)

{

PTCTOG=LED1;//ИзменитьсостояниеLED1(бит0портаPTC)

PTCTOG=LED2;//ИзменитьсостояниеLED2(бит1портаPTC)

delay(60000);//Большаязадержка

PTCTOG=LED1;//ИзменитьсостояниеLED1(бит0портаPTC)

PTCTOG=LED2;//ИзменитьсостояниеLED2(бит1портаPTC)

delay(60000);//Большаязадержка

}

}

Этот пример также показывает, как использовать дополнительные регистры управления портами, которые имеются в данном МК. В частности, использован регистр побитового инвертирования PTCTOG.

Электронные компоненты Freescale >>>

Подробнее о компании Freescale >>>