7.2.2. Режимы работы с внутренним генератором

(Руководство разработчика по микроконтроллерам семейства HCS08)Модуль ICS реализует три режима работы (FEI, FBI и FBILP), в которых внутренний генератор является первичным источником для формирования частоты тактирования. Для настройки этих режимов используются пять битовых полей управления:

- IREFS в регистре ICSC1 — бит выбора источника опорной частоты для FLL. При IREFS = 0 назначается внутренний генератор, при IREFS = 1 — внешний генератор.

- IRCLKEN в регистре ICSC1 — бит разрешения выдачи сигнала ICSIRCLK.

- IREFSTEN в регистре ICSC1 — бит разрешения работы встроенного генератора в режиме STOP.

- ICSTRM — регистр, в котором хранится подстроечное число для внутреннего генератора.

- FTRIM в регистре ICSSC — бит точной подстройки внутреннего генератора.

Внутренний генератор МК обычно работает на частоте от 25 до 41.55 кГц. Посредством программных настроек он может быть установлен на точное значение частоты 31.25 кГц, что соответствует 16 или 32МГц на выходе DCO, или на 39.0625кГц — для 20 или 40МГц на выходе DCO.

Микроконтроллеры HCS08 обладают двумя регистрами для подстройки частоты внутреннего генератора: ICSTRM — регистр грубой подстройки, в котором хранится так называемое подстроечное число TRIM, и ICSSC — регистр состояния, в котором располагается упомянутый выше бит точной подстройки FTRIM. После записи в регистр ICSTRM максимально возможного значения 0xFF внутренний генератор настраивается на низшую частоту 25 кГц, при записи минимально возможного значения — на самую высокую частоту 41.55 кГц. Следует обратить внимание, что эти крайние значения частоты лежат за границами диапазона частот, которые могут использоваться в качестве частоты опорного сигнала для FLL.

Для того чтобы получить на выходе генератора DCO в составе FLL частоту 16 или 32МГц, необходимо настроить внутренний генератор на частоту 31.25кГц. Конкретное значение подстроечного числа, при котором частота внутреннего генератора будет равна 31.25кГц, зависит от случайных флуктуаций технологического процесса. Поэтому для каждого экземпляра МК это число определяется опытным путем во время тестирования МК на заводе-изготовителе и записывается в две ячейки энергонезависимой памяти (0xFFAE для числа FTRIM и 0xFFAF для числа ICSTRM). Записанное производителем в этих ячейках число гарантирует настройку внутреннего генератора на частоту 31.25кГц ±2% во всем диапазоне напряжений питания МК и температуры окружающей среды. Однако для каждого текущего состояния МК (определенное значение напряжения питания и температуры кристалла) внутренний генератор может быть подстроен до значения 31.25кГц ±0.1%.

Для того чтобы выполнить подстройку с использованием числа из энергонезависимой памяти, необходимо после запуска МК под управлением программы произвести копирование ячеек памяти с адресами 0xFFAE и 0xFFAF в соответствующие регистры:

регистрICSSC*/

ICSTRM=NV_ICSTRM;/*Переписатьзначениестаршегобайтаподстроечногочислав

регистрICSTRM*/

Если МК находится в режиме отладки, то выходная частота генератора DCO может быть изменена на иное значение из разрешенного диапазона от 16 до 20МГц другим способом (для МК серий QA, QD и QG). Драйвер наиболее часто используемых для отладки и программирования МК семейства HCS08 интерфейсов P&E Multilink BDM или Multilink Cyclon Pro имеет опцию Advanced Debug/Programming Options (Рис.7.3). Эта опция позволяет установить желаемую частоту генератора DCO прямо с клавиатуры ПК, минуя исполнение программного фрагмента. Однако данная функция драйвера может не оказывать воздействия на модуль второй версии ICSv2.

Рис.7.3. Окно драйвера P&E Multilink/Cyclon, в котором доступна функция настройки частоты ICS.

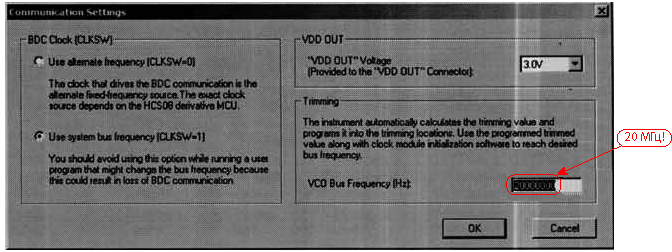

Те читатели, которые используют средства отладки компании Softec, могут изменить частоту генератора DCO из окна Target Connection (см. Рис.3.28,б). При нажатой кнопке Communication Settings откроется окно, которое показано на Рис.7.4.

Рис.7.4. Окно драйвера Softec c функцией настройки частоты ICS.

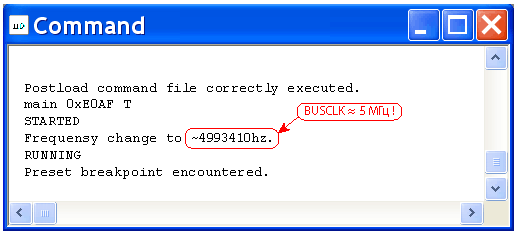

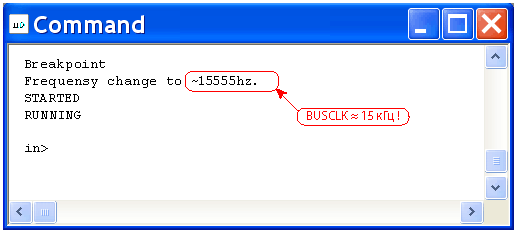

После изменения частоты DCO в этом окне, окно команд отладки покажет новую частоту внутренней шины (Рис.7.5), которая установится в соответствии с начальными установками всех регистров управления модуля ICS после сброса.

Рис.7.5. Окно отладчика Softec отображает событие изменения частоты внутренней шины BUSCLK.

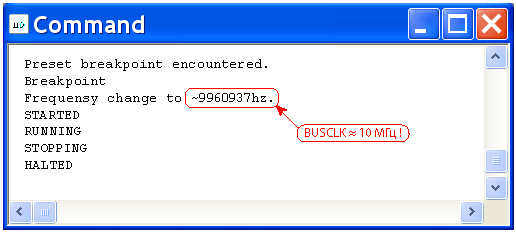

Изменив биты делителя BDIV на 00 (коэффициент деления равен 1), вы получите частоту внутренней шины BUSCLK, близкую к 10МГц (Рис.7.6).

ICSTRM=NV_ICSTRM;/*Переписатьзначениестаршегобайтаподстроечногочислав

регистрICSTRM*/

ICSC2=0;/*BDIV=00*/

Рис.7.6. Окно отладчика Softec отображает новое значение частоты внутренней шины BUSCLK.

После сброса модуль ICS автоматически настраивается на работу в режиме FEI (умножитель частоты работает и использует внутренний генератор) с коэффициентом деления, равным 2 (BDIV = 01). При этом частота шины BUSCLK равна 4МГц. Изменение режима работы модуля ICS производится изменением битов CLKS, IREFS и LP.

Важно, чтобы биты RDIV были записаны той же командой, что и биты CLKS (или ранее), для того, чтобы частота на входе FLL находилась в разрешенном диапазоне 31.25...39.0625кГц.

В режиме FBI выходная частота модуля ISC формируется из частоты внутреннего генератора без участия умножителя FLL. При этом ЦП тактируется очень низкой частотой. Умножитель FLL может быть выключен для снижения энергопотребления. Для этого следует установить бит ICSC2:LP, который переведет модуль ICS в режим FBILP. Режимы FBI и FBILP обычно используются в проектах, которые требуют чрезвычайно низкого потребления энергии. При этом следует помнить, что и расчеты МК будет вести крайне медленно.

Переход в режим FBILP не может быть осуществлен, если МК находится в режиме отладки. В этом случае режим FBILP будет автоматически заменен режимом FBI.

Для перевода модуля ICS в режим FBI следует выполнить следующие установки:

ICSTRM=NV_ICSTRM;/*значениестаршегобайтаподстроечногочиславрегистрICSTRM*/

ICSC1=ICS_FBIbIREFS;/*BDIV=00*/

Фрагмент программы для перевода модуля в режим FBILP:

ICSTRM=NV_ICSTRM/*значениестаршегобайтаподстроечногочиславрегистрICSTRM*/

ICSC1=ICS_FBI|bIREFS;//BDIV=00

ICSC2=bICS_LP;

Помните, что запуск внутреннего генератора после выхода из режима STOP выполняется в течение 60 мкс (100 мкс максимум). Умножитель частоты FLL, после того как он будет выведен под управлением программы из выключенного состояния, требует около 1.5мс для установления желаемой выходной частоты.

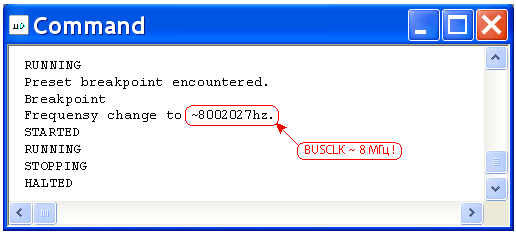

Следующий пример показывает порядок программной настройки модуля ICS на режим FEI (FLL с опорной частотой от внутреннего генератора), частота на выходе DCO равна 16МГц. На Рис.7.7 показано окно отладчика, в котором отображается частота шины МК после исполнения данного программного фрагмента. Измеренная отладчиком частота шины BUSCLK = 8.002027МГц, что соответствует 16.004054МГц на выходе модуля ICSOUT. Отклонение от номинального значения 16.0МГц составляет 0.25%.

Пример 7.1. Инициализация модуля ICS в режим FEI

#include

#include

#include

voidmain(void)

{

Unsignedinttemp;

SOPT1=bBKGDPE;/*Конфигурирование:разрешениефункцииBDMдлявыводаBKGD*/

ICSSC=NV_FTRIM;//ПереписатьзначениеFTRIMврегистрICSSC

ICSTRM=NV_ICSTRM//Переписатьзначениестаршегобайтаподстроечногочисла

ICSC1=ICS_FLL|bIREFS;/*ВыбратьрежимFEI*/

ICSC2=BDIV_1;/*ICSOUT=DCOOUT/1*/

PTBDD=0xFF;/*ВыходыпортаPTB–навывод*/

PTBD=0xC0;/*ВыключитьсветодиодыLED1иLED2*/

while(1)

{

PTBD_PTBD6=0;/*Включитьсветодиод*/

for(temp=3000;temp;temp--);/*Программнаязадержка*/

PTBD_PTBD6=1;/*Выключитьсветодиод*/

for(temp=3000;temp;temp--);/*Программнаязадержка*/

}

}

Рис.7.7. Окно отладчика Softec отображает установленное значение частоты BUSCLK=8 МГц.

Следующий пример показывает, как инициализировать модуль ICS в составе МК MC9S08QG8 на режим FBILP (тактирование ЦП от внутреннего генератора при выключенном умножителе FLL). Обратите внимание на необходимое снижение числа циклов в программной задержке, которая используется для мигания светодиода. В предыдущем примере значение счетчика циклов для задержки было равно 3000, а в текущем примере — всего 6. Действительно, при тактировании ЦП от внутреннего генератора частота должна снизиться в 512 раз (коэффициент умножения FLL в выбранной модели МК).

Пример 7.2. Инициализация модуля ICS в режим FBILP

#include

#include

#include

voidmain(void)

{

Unsignedinttemp;

SOPT1=bBKGDPE;/*Конфигурирование:разрешениефункцииBDMдлявыводаBKGD*/

ICSSC=NV_FTRIM;/*ПереписатьзначениеFTRIMврегистрICSSC*/

ICSTRM=NV_ICSTRM/*Переписатьзначениестаршегобайтаподстроечногочисла*/

ICSC1=ICS_FLL|bIREFS;/*ВыбратьрежимFEI*/

ICSC2=BDIV_1;/*ICSOUT=DCOOUT/1*/

PTBDD=0xFF;/*ВыходыпортаPTB–навывод*/

PTBD=0xC0;/*ВыключитьсветодиодыLED1иLED2*/

while(1)

{

PTBD_PTBD6=0;/*Включитьсветодиод*/

for(temp=3000;temp;temp--);/*Программнаязадержка*/

PTBD_PTBD6=1;/*Выключитьсветодиод*/

for(temp=3000;temp;temp--);/*Программнаязадержка*/

}

}

На Рис.7.8 показано окно отладчика с измеренной частотой после исполнения программного кода Примера 7.2. Частота внутренней шины составляет 15.555 кГц, что соответствует 31.11 кГц на выходе модуля ICS. Ошибка настройки относительно номинального значения 31.25 кГц составляет 0.448%.

Рис.7.8. Окно отладчика Softec отображает установленное значение частоты BUSCLK =1 5.555 кГц.

Электронные компоненты Freescale >>>

Подробнее о компании Freescale >>>