2.1.9. Режим отладки

(Руководство разработчика по микроконтроллерам семейства HCS08)Все МК семейства HCS08 имеют в своем составе модуль внутрисхемной отладки, который позволяет:

- программировать МК, т.е. заносить программу в энергонезависимое резидентное флэш-ПЗУ;

- отлаживать управляющую программу, т.е. проверять правильность исполнения программы под управлением ПК.

Модуль внутрисхемной отладки осуществляет связь с ПК по однопроводному двунаправленному интерфейсу. Модуль состоит из двух блоков:

- контроллер отладки (BDC) — реализует доступ к внутренним ресурсам ЦП на аппаратном уровне, т.е. без остановки исполнения отлаживаемой программы. Контроллер BDC также поддерживает протокол обмена с ПК по однопроводному интерфейсу;

- модуль отладки (DBG) — реализует дополнительные функции отладки. Его аппаратная реализация предусматривает наличие двух или трех (в МК серии QE) 16-битных цифровых компараторов для «установки» контрольных точек на аппаратном уровне, а также собственный 8-уровневый 16-битный стек.

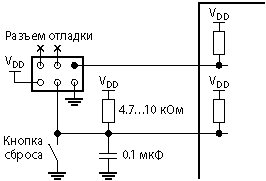

Связь между компьютером и отлаживаемым МК осуществляется посредством специального устройства — адаптера BDM. В качестве последнего рекомендуется использовать серийно выпускаемые изделия, такие как USB BDM Multilink Cable или Cyclon PRO от компании P&E Microcomputer Systems, или любое другое устройство, поддерживающее интерфейс BDM. Адаптер BDM — это специальный электронный модуль, который преобразует сигналы однопроводного интерфейса отладки МК в стандартный последовательный протокол USB для компьютера. Адаптер BDM соединяется с МК на плате проектируемого изделия через стандартный 6-выводной разъем, цоколевка которого приведена на Рис.2.11. Рекомендованная схема подключения МК к выводам разъема представлена на Рис.2.12.

| BKGD1 | ♦ | • | 2GND | |

| n.c.3 | • | • | 4RESET | |

| n.c.5 | • | • | 6VDD | |

Рис.2.11. Цоколевка разъема BDM на плате с микроконтроллером HCS08.

Рис.2.12. Рекомендуемая схема подключения МК к выводам разъема адаптера BDM.

В некоторых моделях МК вывод BKGND/MS мультиплексирован с однонаправленной линией порта вывода, а вывод RESET — с однонаправленной линией порта ввода. В таких МК функции BKGND/MS и RESET для рассматриваемых выводов разрешаются или запрещаются битами BKGDPE и RSTPE в регистрах SOPT и SOPT1.

2.1.9.1. Вывод BKGND/MS

Вывод BKGND/MS используется для подключения МК HCS08 к адаптеру BDM. Вывод BKGND/MS предназначен для реализации сразу двух функций: соединения с внешним устройством отладки (BKGND) и выбора режима работы МК (MS).

В состоянии сброса микроконтроллера вывод BKGND/MS используется для выбора режима работы МК. Адаптер BDM, подключенный к 6-выводному разъему отладки, принудительно устанавливает логический 0 на выводе BKGND/MS, заставляя МК перейти в режим отладки. Если адаптер BDM не подключен, то вывод BKGND/MS через подтягивающий резистор автоматически подключается к напряжению питания. При ВЫСОКОМ логическом уровне на входе BKGND/MS МК переходит в пользовательский режим работы. В этом режиме МК будет исполнять программу управления только под управлением собственных ресурсов, без участия модуля отладки. МК осуществляет переход в пользовательский режим в момент выхода из режима сброса. До вывода МК из состояния сброса изменение уровня сигнала на выводе BKGND/MS позволяет сколь угодно раз переназначать режим работы МК, выбирая отладочный или пользовательский режим работы. Но после выхода из состояния сброса МК запоминает назначенный режим работы. Изменение этого режима может быть произведено только во время принудительной установки МК в состояние сброса посредством подачи НИЗКОГО логического уровня на вход RESET/RST микроконтроллера.

При работе в режиме отладки вывод BKGND используется в качестве двунаправленной линии связи посредством адаптера BDM с компьютером. МК поддерживает собственный полудуплексный протокол связи. При частоте внутренней шины 20МГц скорость обмена составляет 1.25МБ/с.

2.1.9.2. Контроллер фоновой отладки BDC

Встроенный контроллер фоновой отладки BDC отвечает за связь МК с компьютером, выполнение поступающих от ПК команд отладки, доступ к внутренним регистрам ЦП и за обработку контрольных точек.

Все команды, которые исполняет BDC, делятся на две группы: команды неагрессивного доступа и команды агрессивного доступа. Неагрессивные команды в основном используются для управления самим BDC, а также для чтения/записи резидентной памяти МК.

Контроллер BDC выполняет команды неагрессивного доступа без остановки выполнения отлаживаемой программы. При этом используются «холостые» машинные циклы внутренних магистралей, когда исполняемая прикладная программа не производит обращения к памяти. Если такие «холостые» циклы не возникают в течение 128 машинных циклов, то блок BDС захватывает последующие циклы для выполнения поступившей команды отладки. При этом выполнение прикладной программы слегка притормаживается. Обсуждаемые так называемые аппаратные команды отладки могут поступать в контроллер BDC от ПК не чаще, чем 1 раз в 150 машинных циклов.

Команды агрессивного доступа используются для чтения/записи регистров ЦП, для останова по контрольным точкам, а также для операций над ячейками резидентной памяти и управления режимами BDC. Команды агрессивного доступа выполняются с обязательным остановом исполнения отлаживаемой программы.

В процессе сеанса отладки ПО необходимые команды управления BDC формируются и передаются в МК автоматически. Эти действия выполняются специальным программным обеспечением (интегрированной средой разработки CodeWarrior), установленным на персональном компьютере. Все, что необходимо сделать, — начать сеанс отладки, используя установленное ПО CodeWarrior, и следить за ходом исполнения программы и за состоянием переменных.

2.1.9.3. Модуль расширения функций отладки DBG

Модуль отладки DBG содержит два компаратора с защелкой (А и В), которые обеспечивают девять режимов останова по контрольным точкам. В момент останова запускается сеанс обмена между МК и компьютером.

Компаратор адреса А присоединен к 16-битной шине адреса. Компаратор В по командам контроллера BDC может сравнивать либо 16-битные адреса, либо 8-битные данные. В МК серии QE (серия Flexis) дополнительный компаратор C подключен к шине адреса. Гибкость настройки модуля DBG позволяет найти любые ошибки в программном обеспечении. Девять комбинаций событий, по которым можно осуществить останов исполнения отлаживаемой программы в контрольной точке, приведены в Табл.2.8.

Таблица2.8. Комбинации событий для фиксации контрольных точек модулем DBG

| Условие фиксации контрольной точки | Описание режима |

|---|---|

| Только А | Контрольная точка устанавливается, когда код на шине адреса совпадает с кодом на входах компаратора А во время процедуры записи или чтения (назначается отдельной опцией). |

| А или B | Контрольная точка устанавливается, когда код на шине адреса совпадает с кодом на входах компараторов А или B во время процедуры записи или чтения. |

| А, потом B | Контрольная точка устанавливается, когда сначала код на шине адреса совпадает с кодом на входах компаратора А во время процедуры записи или чтения, а затем другой код на шине адреса совпадает с кодом на входах компаратора B во время процедуры записи или чтения. |

| А и B (данные) | Контрольная точка устанавливается, когда одновременно совпадают код на шине адреса с кодом на входах компаратора А и код на шине данных с кодом на входах компаратора B. Этот режим может использоваться, когда необходимо «поймать» момент записи или чтения определенных данных. |

| А и не B (данные) | Контрольная точка устанавливается, когда одновременно совпадают код на шине адреса с кодом на входах компаратора А, а код на шине данных не совпадает с кодом на входах компаратора B. Этот режим может использоваться, когда необходимо «поймать» момент записи или чтения данных, не совпадающих с заданными. |

| Только B (стек) | Контрольная точка устанавливается, когда код на шине адреса совпадает с кодом на входах компаратора B во время процедуры записи или чтения. Помимо установки контрольной точки, текущее значение шины данных записывается во внутренний стек. |

| А потом B (стек) | Контрольная точка устанавливается, когда сначала код на шине адреса совпадает с кодом на входах компаратора А во время процедуры записи или чтения, а затем код на шине адреса совпадает с кодом на входах компаратора B во время процедуры записи или чтения. Помимо установки контрольной точки, текущее значение шины данных записывается во внутренний стек. |

| В диапазоне | Установка контрольной точки происходит, если код на шине адреса больше или равен значению на входах компаратора А и меньше или равен значению на входах компаратора B. |

| Вне диапазона | Установка контрольной точки происходит, если код на шине адреса меньше или равен значению на входах компаратора А и больше или равен значению на входах компаратора B. |

В составе модуля отладки DBG также имеется собственная 16-битная 8-уровневая стековая память, позволяющая хранить зафиксированные в определенные моменты времени адреса и данные. Это позволяет посмотреть в программе, установленной на ПК, по какому пути осуществляются вычисления, в том числе посмотреть изменения регистров и ячеек памяти. В разделе 3.5 будет подробно рассмотрено, как использовать функции модуля BDG.

2.2. Программная модель Flexis

Среди достаточно большого количества моделей МК семейства HCS08 выделяется подсемейство Flexis. Это подсемейство объединяет полностью совместимые на аппаратном и программном уровнях 8-битные МК с процессорным ядром HCS08 и 32-битные МК с процессорным ядром ColdFireV1. Микроконтроллеры HCS08 Flexis отличаются увеличенным объемом резидентной флэш-памяти программ (модели MC9S08QE64/96/128, MC9S08JM60, MC9S08AC64/96/128).

Для адресации встроенной памяти, объем которой превышает 64 КБ, МК HCS08 Flexis снабжены специальным модулем управления памятью MMU (Memory Management Unit). Этот модуль позволяет расширить объем адресуемой центральным процессором памяти до 4МБ. Исходные 64КБ памяти разбиты на 4 страницы по 16КБ (Рис.2.13). Страница с номером 2, начиная с адреса 0x8000 до адреса 0xBFFF, ссылается на одну из дополнительных страниц, выбранных с помощью MMU. Выбор дополнительной страницы происходит по значению регистра PPAGE. Если PPAGE = 0, то будет реализовываться обращение к нулевой странице флэш-памяти. При указании на адрес 0x8000 на самом деле произойдет ссылка на адрес 0x00000, адрес 0x8001 будет ссылаться на 0x00001 и т.д. (см. Рис.2.13).

| PPAGE | Доступ методом страничной адресации | Прямой доступ | |

|---|---|---|---|

| 0x00000 0x0007F | 0 | Флэш-память 16КБ | Регистры специальных функций (нулевая страница) |

| 0x00080 0x000FF | ОЗУ (нулевая страница) 128 Б | ||

| 0x00100 0x017FF | ОЗУ (резервная область) 5888Б | ||

| 0x01800 0x0187F | Регистры специальных функций (старшая страница) | ||

| 0x01880 0x0207F | ОЗУ (резервная область) 2048Б | ||

| 0x02080 0x03FFF | Флэш-память 8064Б | ||

| 0x04000 0x07FFF | 1 | Флэш-память 16КБ | |

| 0x08000 0x0BFFF | 2 | Флэш-память 16КБ | Окно страничной адресации |

| 0x0C000 0x0FFFF | 3 | Флэш-память 16КБ | |

| 0x10000 0x13FFF | 4 | Флэш-память 16КБ | |

| 0x14000 0x17FFF | 5 | Флэш-память 16КБ | |

| 0x18000 0x1BFFF | 6 | Флэш-память 16КБ | |

| 0x1C000 0x1FFFF | 7 | Флэш-память 16КБ | |

| 0x20000 0xFFFFF | 8...255 | Зарезервировано | |

Рис.2.13. Деление адресного пространства на страницы, адресуемые модулем MMU.

Страницы с 0-й по 3-ю адресуются прямо посредством 16-битного адреса. Такой механизм адресации называется линейным, он характерен для всех HCS08 с объемом памяти менее 64КБ. Обращение к ячейке памяти линейно адресуемого адресного пространства может быть осуществлено с помощью любого из ранее изученных способов адресации.

Страницы памяти с 4-й по 255-ю расположены по адресам, коды которых не могут разместиться в 16-битном формате. Для обращения к этим страницам памяти используется 24-битный формат представления адреса. Модуль MMU позволяет обратиться к ячейкам с 24-битным адресом двумя способами:

- Страничная адресация. При этом способе номер активной страницы записывается в регистр PPAGE. Далее к ячейкам памяти из этой страницы обращаются с использованием способов адресации для линейно адресуемого адресного пространства, но учитывая, что начальный адрес любой текущей страницы равен 0x8000, а конечный — 0xBFFF.

- Линейная адресация через 24-битный указатель LAP2:LAP1:LAP0. При этом способе адресации адрес, по которому будет происходить обращение, должен быть предварительно загружен в три регистра LAP2, LAP1 и LAP0. Образованный таким образом трехбайтный регистр и есть регистр индексной адресации для расширенного адресного пространства.

| Линейный адрес | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Бит регистра | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Название регистра | LAP2 | LAP1 | LAP0 | |||||||||||||||||||||

Страничная адресация обычно используется в процессе исполнения программного кода, поскольку счетчик PC имеет разрядность 16 и не позволяет линейно адресовать ячейки памяти, адреса которых требуют для своего представления большего числа двоичных разрядов. Линейная адресация с 24-битным адресом используется для операций чтения/записи данных в определенные ячейки памяти расширенного адресного пространства.

Адресация памяти аппаратными средствами блока MMU происходит с помощью специальных регистров. Если 24-битный адрес записан в регистр LAP (LAP образован из трех регистров — LAP2:LAP1:LAP0), то для чтения или записи данных необходимо использовать регистры LWP, LBP и LB:

| LWP | Используется для записи/чтения двухбайтного слова, начальный адрес которого записан в регистре LAP. После выполнения операции чтения/записи содержимое LAP автоматически увеличивается на 2. |

| LBP | Используется для чтения/записи однобайтной ячейки, адрес которой записан в регистре LAP. После выполнения операции чтения/записи содержимое LAP увеличивается на 1. |

Регистры LWP и LBP имеют адреса 0x007C и 0x007D. Доступ к 16-битному слову осуществляется командами двухбайтного обмена LDHX и STHX по адресу LWP. Для доступа к 8-битному слову могут быть использованы любые команды обмена с указанием адреса LBP.

| LB | Используется для записи/чтения ячейки памяти, адрес которой записан в регистре LAP. После чтения содержимое LAP не увеличивается! Адрес регистра LB — 0x007E. |

| LAPAB | Предназначен для изменения кода адреса, который хранится в LAP. Операция записи в регистр LAPAB числа в дополнительном коде сопровождается вычислением нового значения 24-битного адреса в регистре LAP: LAP=LAP+LAPAB. В данный регистр можно только записывать, при попытке чтения возвращается 0. Адрес регистра LBAB — 0x007F. |

Примеры:

1.Доступ к переменной по адресу $10000 (ассемблер)

var:DS1

ORGROMStart

MOV#$01,LAP2;LAP2=$01

CLRLAPl;LAPl=$00

CLRLAPO;LAP0=$00,приэтом24-битныйLAP=$10000

LDALB;ЗагрузитьваккумуляторАсодержимоеячейки$10000

2.Доступ к переменный по адресу 0x10000 (C)

temp=LB;//Загрузитьвпеременнуюtempсодержимоеячейки0x10000

3.Работа с LAP-регистрами: программный код на языке ассемблер

MOV#$12,LAPl;LAPl=$12

MOV#$34,LAP0;LAP0=$34,LAP=$01234

LDHXLWP;ЗагрузитьвHX2байта,начинаясадреса$1234

MOV#2,LAPAB;Прибавить2кLAP

MOV#-6,LAPAB;Вычесть6изLAP

Тот же пример на языке С

Var16=LWP;//загрузить2байта,начинаясадреса0x1234,впеременнуюvar16

LAPAB=2;//прибавить2кLAP

LAPAB=-6;//вычесть6изLAP

4.Доступ к однобайтному массиву данных на C

LAP=array_name;

LAPAB=index;

temp=LB;//Присвоитьtempзначениеэлементамассивасномеромindex

//Длямассивовбольше127байт

LAP=array_name+index;//LAP=arrayaddress+index

temp=LB;//Присвоитьtempзначениеэлементамассивасномеромindex

Перечисленные регистры специальных функций модуля MMU располагаются в нулевой странице, что позволяет использовать для манипуляций чтения/записи ячеек памяти с 24-битным адресом короткие команды с прямой адресацией, в том числе команд типа MOV. В сочетании с автоматическим изменением адреса в 24-битном регистре индексной адресации такое расположение позволяет сократить время доступа к ячейкам памяти расширенного адресного пространства.

Для работы с подпрограммами, коды которых располагаются в расширенном адресном пространстве, введены две дополнительные команды:

| CALL | Осуществляет вызов подпрограммы, используя страничную адресацию. Синтаксис команды: CALL <страница>, <16-битный адрес>. В процессе исполнения команды CALL в стек дополнительно записывается регистр PPAGE, что позволяет сначала осуществить вызов подпрограммы из любой страницы памяти, а затем — возврат к основной программе, также находящейся в любой произвольной странице памяти. |

| RTC | Команда возврата из подпрограммы. Действует точно так же, как RTS, но дополнительно возвращает значение регистра PPAGE из стека. |

2.3. Номенклатура МК семейства HCS08

На Рис.2.14 представлен формат условного обозначения МК семейства HCS08.

| MC | 9 | S08 | QD | 4 | ||

|---|---|---|---|---|---|---|

| Размер флэш-памяти программ (4КБ) | ||||||

| Обозначение модели (QD) | ||||||

| Обозначение семейства (HCS08 – буквы HC в условном обозначении пропущены) | ||||||

| Тип памяти программ | ||||||

| Стандартный префикс, обозначает выпуск серийного изделия |

Рис.2.14. Обозначение МК семейства HCS08.

Современная международная система обозначений включает в себя три возможных типа программной памяти: 7 — OTP ROM (однократно программируемая пользователем память), 8 — EEPROM (побайтно электрически стираемая и побайтно электрически программируемая память), 9 — флэш-память (электрически стираемая блоками и электрически программируемая память). МК семейства HCS08 выпускаются только с флэш-памятью программ.

Обозначение модели используется для определения конфигурации МК в пределах семейства HCS08. Первая буква определяет общую группу — серию, как показано в Табл.2.9.

Таблица2.9. Серии МК в составе семейства HCS08

| Серия | Краткая характеристика |

|---|---|

| A | Для применения в автомобилестроении и промышленности (напряжение питания 2.7...5.5В). AC — устройства Flexis, большое количество выводов (до 64), усовершенствованные периферийные модули и функции защиты (секретность кода). AW — большое количество выводов (до 64). |

| D | Для применения в автомобилестроении и промышленности (напряжение питания 2.7...5.5В). DN — устройства с дополнительным блоком памяти EEPROM. DV — устройства с встроенным CAN-контроллером. DZ — с памятью EEPROM и CAN-контроллером. |

| E | Для применения в автомобилестроении, со встроенным LIN-контроллером. EL — c памятью EEPROM. EN — без памяти EEPROM. |

| G | Общего применения (напряжение питания 1.6...3.6В). GB — корпуса с большим количеством выводов (от 64). GT — корпуса с небольшим количеством выводов (от 32 до 64). |

| J | С встроенными протоколами связи. JM — устройства Flexis со встроенным контроллером USB2.0 JR — со встроенным передатчиком на частоте 27МГц. |

| L | Для устройств с заказными ЖК-индикаторами. LC — устройство с низким напряжением питания и модулем драйвера ЖК-дисплея до 160 сегментов |

| Q | Общего назначения. QA — напряжение 1.8...3.6В, низкая стоимость. QE — устройства Flexis. QD — напряжение питания 2.7...5.5В, самые дешевые из семейства HCS08. QG — напряжение 1.8...3.6В, низкая стоимость. |

| S | Малые корпуса, общего назначения (напряжение питания 2.7...5.5В). SG — корпус 8...28 выводов, от 4 до 32 КБ флэш-памяти. SH — корпус 8...24 выводов, улучшенный вариант устройств серии QG. SL — устройства для автомобилестроения с памятью EEPROM и LIN-контроллером. |

| R | Для удаленного сбора данных и систем распределенного управления. RC, RD, RE, RG. |

2.4. Доступные модели

Ниже представлена краткая информация об имеющихся моделях МК семейства HCS08.

Таблица2.10. Конфигурация МК семейства HCS08

| Модель МК | VDD* | Флэш-память [КБ] | ОЗУ [байт] | EEPROM [байт] | fBUS [МГц] | Ввод/ вывод** | Таймеры*** | IR | SCI | USB | CAN | I2C | SPI | АЦП**** | Аналоговый компаратор | Корпус |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| AC8 AW8A | H | 8 | 768 | нет | 20 | 38 | 3 — 16 бит 4+2+2 CCP | нет | 2 | нет | нет | 1 | 1 | 8/10 бит | нет | LQFP32 SDIP42 LQFP44 QFN48 |

| AC16 AW16A | H | 16 | 1024 | нет | 20 | 38 | 3 — 16 бит 4+2+2 CCP | нет | 2 | нет | нет | 1 | 1 | 8/10 бит | нет | LQFP32 SDIP42 LQFP44 QFN48 |

| AW16 AW32 AW48 AW60 | H | 16 32 48 60 | 1024 2048 2048 2048 | нет | 20 | 34 54 54 54 | 2 — 16 бит 6+2 CCP | нет | 2 | нет | нет | 1 | 1 | 16/10 бит | нет | LQFP44 QFN48 LQFP64 QFN64 |

| DN16 DN32 DN48 DN60 | H | 16 32 48 60 | 1024 2048 3072 4096 | 512 1024 1536 2048 | 20 | 54 54 54 54 | 2 — 16 бит 6+2 CCP | нет | 2 | нет | нет | 1 | 1 | 16/10 бит 24/10 бит 24/10 бит 24/10 бит | 2 | LQFP32 LQFP44 LQFP64 QFN64 |

| DV16 DV32 DV48 DV60 | H | 16 32 48 60 | 1024 2048 3072 4096 | нет | 20 | 54 54 54 54 | 2 — 16 бит 6+2 CCP | нет | 2 | нет | 1 | 1 | 1 | 16/10 бит 24/10 бит 24/10 бит 24/10 бит | 2 | LQFP32 LQFP44 LQFP64 QFN64 |

| DZ16 DZ32 DZ48 DZ60 | H | 16 32 48 60 | 1024 2048 3072 4096 | 512 1024 1536 2048 | 20 | 54 54 54 54 | 2 — 16 бит 6+2 CCP | нет | 2 | нет | 1 | 1 | 1 | 16/10 бит 24/10 бит 24/10 бит 24/10 бит | 2 | LQFP32 LQFP44 LQFP64 QFN64 |

| EL16 EL32 | H | 16 32 | 1024 | 512 | 20 | 26 | 2 — 16 бит 4+2 CCP | нет | 1 | нет | нет | 1 | 1 | 16/10 бит | 2 | TSSOP20 TSSOP28 |

| EN16 EN32 | H | 16 32 | 512 1024 | нет | 20 | 39 | 1 — 16 бит 4 CCP | нет | 1 | нет | нет | 1 | 1 | 12/10 бит | 1 | LQFP32 LQFP48 |

| GB32A GB60A | L | 16 32 | 2048 4096 | нет | 20 | 56 | 2 — 16 бит 3+5 CCP | нет | 2 | нет | нет | 1 | 1 | 8/10 бит | нет | QFP64 |

| GT8A GT16A GT32A GT60A | L | 8 16 32 60 | 2048 4096 2048 4096 | нет | 20 | 39 | 2 — 16 бит 3+2 CCP | нет | 1 1 2 2 | нет | нет | 1 | 1 | 8/10 бит | нет | QFN32 SDIP42 QFN44 QFN48 |

| JM32 JM60 | H | 32 60 | 2048 4096 | нет | 24 | 51 | 2 — 16 бит 6+2 CCP | нет | 2 | 1 | нет | 1 | 2 | 12/12 бит | 1 | LQFP64 QFN48 QFP64 QFP44 |

| LC36 LC60 | L | 36 60 | 4096 | нет | 20 | 24 | 1 — 16 бит 2 CCP | нет | 1 | нет | нет | 1 | 2 | 8/12 бит | 1 | LQFP64 LQFP80 |

| QA2 QA4 | L | 2 4 | 160 256 | нет | 20 | 6 | 1 — 16 бит + 1 — 8 бит 2+0 CCP | нет | нет | нет | нет | нет | нет | 4/10 бит | нет | DIP8 SOIC8 |

| QD2 QD4 | H | 2 4 | 128 256 | нет | 10 | 6 | 2 — 16 бит 2+1 CCP | нет | нет | нет | нет | нет | нет | 4/10 бит | нет | DIP8 SOIC8 |

| QE4 QE8 QE64 QE96 QE128 | L | 4 8 64 96 128 | 256 512 4096 6016 8064 | нет | 20 20 25 25 25 | 26 26 54 70 70 | 2 — 16 бит 3+3 CCP | нет | 1 1 2 2 2 | нет | нет | 1 1 2 2 2 | 1 1 2 2 2 | 10/12 бит 10/12 бит 22/12 бит 24/12 бит 24/12 бит | 2 | DIP16 TSSOP16 SOIC20 LQFP32 LQFP64 LQFP80 QFP48 |

| 3 — 16 бит 3+3+6 CCP | ||||||||||||||||

| QG4 QG8 | L | 4 8 | 256 512 | нет | 10 | 12 | 1 — 16 бит + 1 — 8 бит 2+0 CCP | нет | 1 | нет | нет | 1 | 1 | 8/10 бит | 1 | DIP8 DFN8 DIP16 QFN16 TSSOP16 |

| RC8 RC16 RC32 RC60 | H | 8 16 32 60 | 1024 1024 2048 2048 | нет | 8 | 39 | 1 — 16 бит 2 CCP | 1 | нет | нет | нет | нет | нет | нет | 1 | LQFP32 LQFP44 |

| RD8 RD16 RD32 RD60 | H | 8 16 32 60 | 1024 1024 2048 2048 | нет | 8 | 39 | 1 — 16 бит 2 CCP | 1 | 1 | нет | нет | нет | нет | нет | нет | DIP28 SOIC28 LQFP32 LQFP44 |

| RE8 RE16 RE32 RE60 | H | 8 16 32 60 | 1024 1024 2048 2048 | нет | 8 | 39 | 1 — 16 бит 2 CCP | 1 | 1 | нет | нет | нет | нет | нет | 1 | DIP28 SOIC28 LQFP32 LQFP44 |

| RG32 RG60 | H | 32 60 | 1024 2048 | нет | 8 | 39 | 1 — 16 бит 2 CCP | 1 | 1 | нет | нет | нет | нет | нет | 1 | LQFP32 LQFP44 |

| SG4 SG8 SG16 SG32 | H | 4 8 16 32 | 256 512 1024 1024 | нет | 20 | 18 18 26 26 | 2 — 16 бит + 1 — 8 бит 2+2+0 CCP | нет | 1 | нет | нет | 1 | 1 | 12/10 бит 12/10 бит 16/10 бит 16/10 бит | 1 | SOIC8 TSSOP16 TSSOP20 TSSOP28 |

| SH4 SH8 | H | 4 8 | 256 512 | нет | 20 | 17 | 2 — 16 бит + 1 — 8 бит 2+2+0 CCP | нет | 1 | нет | нет | 1 | 1 | 12/10 бит | 1 | TSSOP16 TSSOP20 DIP20 QFN24 |

| SL8 SL16 | H | 8 16 | 512 | 256 | 20 | 26 | 2 — 16 бит 2+2 CCP | нет | 1 | нет | нет | 1 | 1 | 16/10 бит | 1 | TSSOP20 TSSOP28 |

| * | Символом Н обозначены МК с диапазоном напряжений питания от 2.7 до 5.5 В, символом L — от 1.8 до 3.6 В. |

| ** | Число линий ввода/вывода, в том числе мультиплексированных. |

| *** | Для таймеров указаны следующие характеристики: число таймеров — разрядность счетчика временной базы, число каналов IC/OC/PWM (CCP) в каждом из таймеров. |

| **** | Для АЦП указаны следующие характеристики: число каналов/число битов преобразования. |

2.5. Цоколевка корпусов МК

Ниже на рисунках представлены цоколевки корпусов микроконтроллеров семейства HSC08.

| PTA5/IRQ/TCLK/RESET | 1 | 8 | PTA0/KBIP0/TPMCH0/ADP0/ACMP+ | |||

| PTA4/ACMPO/BKGD/MS | 2 | 7 | PTA1/KBIP1/ADP1/ACMP– | |||

| VDD | 3 | 6 | PTA2/KBIP2/SDA/ADP2 | |||

| VSS | 4 | 5 | PTA3/KBIP3/SCL/ADP3 | |||

DIP8/DFN8/SOIC8

Электронные компоненты Freescale >>>

Подробнее о компании Freescale >>>