11.3. Интерфейс SCI

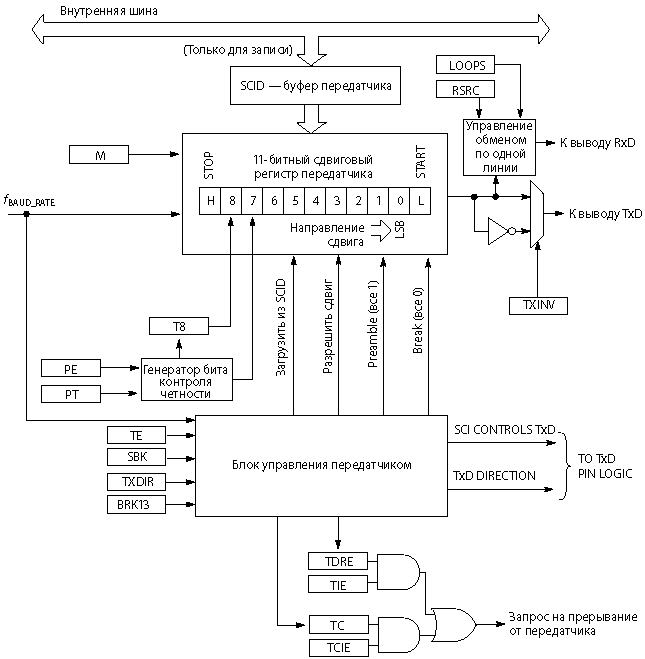

(Руководство разработчика по микроконтроллерам семейства HCS08)Передатчик (Рис.11.11) состоит из сдвигового регистра TSR (Transmit Shift Register) с параллельным входом и последовательным выходом и блока управления, который определяет режим работы передатчика и линии выхода TxD.

Рис.11.11. Структурная схема передатчика SCI.

Аппаратные средства модуля SCI обеспечивают возможность независимой работы передатчика и приемника, поэтому каждый из них имеет собственный бит разрешения работы. Для активизации работы передатчика следует установить бит TE в регистре управления SCIC2. Далее следует корректно настроить подсистему передатчика.

Размер одного кадра данных определяется битом M регистра SCIC1. Если M = 0, то передается 8 бит данных плюс один старт-бит и один стоп-бит (всего 10 бит). Если M = 1, то передаются 9 бит данных плюс старт-бит и стоп-бит (всего 11 бит).

Передатчик может быть сконфигурирован на автоматическую генерацию бита контроля четности. Это достигается установкой бита PE в регистре SCIC1. Бит контроля четности, в свою очередь, может быть посчитан и установлен несколькими способами. Выбор способа установки определяется битом PT в регистре управления SCIC1. Если PT = 0, то бит контроля четности равен 1, если в передаваемом слове нечетное число единиц, если же PT = 1, то бит контроля четности равен 1, если в передаваемом слове четное число единиц. Передаваемое слово — это исходное слово, т.е. без присоединенного бита контроля четности.

Перед передачей байта данных необходимо программно проверить состояние бита готовности буфера передатчика к приему новых данных. В этом случае бит TDRE регистра SCIS1 будет установлен в 1. Флаг TDRE = 1 информирует о том, что буфер передатчика пуст, и в него может быть записан новый байт данных. Если бит TDRE = 1, то при записи данных в регистр SCID начинается их передача.

Если передатчик работает в режиме передачи 9 бит данных (SCIC1:M = 1), то девятый бит определяется состоянием бита T8 регистра SCIC3. Он должен быть определен до начала сеанса передачи данных, иначе будет использоваться предыдущее значение бита T8.

SCID=0x50;//Передачачисла0x50(0x150в9-битномрежиме)

Как только в регистр SCID записываются данные, триггер TDRE сбрасывается, информируя программу о том, что буфер передатчика полон. Содержимое регистра данных SCID автоматически переносится в программно недоступный сдвиговый регистр TSR, и начинается передача данных. Данные передаются по линии TxD, которая автоматически настраивается на вывод при включении передатчика SCI. Скорость обмена устанавливается в регистре SCIBD. Обратите внимание, что данные выставляются на линию, начиная с младшего бита.

Как только данные из программно доступного буфера приемника SCID поступят в программно недоступный сдвиговый регистр TSR, установится бит TDRE. Это означает, что регистр SCID оказался пуст, и в него можно записывать очередной байт данных. Этот новый байт автоматически запишется в сдвиговый регистр TSR, как только закончится выдача на линию текущего байта данных.

Как только все данные из регистра TSR передадутся по линии TxD, установится флаг завершения передачи TC в регистре SCIS1.

Для демонстрации простоты программного обслуживания модуля SCI рассмотрим небольшой Пример 11.6. В нем показано, как настроить передатчик модуля SCI и как передать символ «H» по последовательному интерфейсу через COM-порт в персональный компьютер. С помощью стандартной программы Windows, которая носит название HyperTerminal, можно увидеть данные, которые посылаются микроконтроллером демонстрационной платы DEMO9S08QG8 и принимаются компьютером. Не забудьте соединить демонстрационную плату и компьютер специальным кабелем!

Пример 11.6. Передача одного символа по SCI

//ДемонстрационнаяплатаDEMO9S08QG8

#include

#include"derivative.h"/*includeperipheraldeclarations*/

#include"hcs08.h"/*Этонашфайлсобъявлениями!*/

voidmain(void)

{

SOPT1=bBKGDPE;//ВключениелинииотладкиBKGD

//ПослесбросаBUSCLK=4МГц

SCIBD=26;//СкоростьпередачиSCI:4МГц/(16*26)=9615бит/с

SCIC2=bTE;//Включениепередатчика

SCID='H';//Пересылкасимвола'H'поинтерфейсуSCI

while(1);

}

Перед запуском данного примера удалите перемычку COM_EN! Эта перемычка соединяет линию PTA4 микроконтроллера MC9S08QG8 с входами FORCEON и FORCEOFF микросхемы MAX3218. Эта линия используется модулем BDM для включения и выключения микросхемы MSX3218, которая генерирует сигналы в COM-порт.

В следующем примере показано применение простой функции пересылки строки null terminated по интерфейсу SCI. В этой функции не используются прерывания.

Пример 11.7. Передача строки по SCI

//ДемонстрационнаяплатаDEMO9S08QG8

#include

#include"derivative.h"/*includeperipheraldeclarations*/

#include"hcs08.h"/*Этонашфайлсобъявлениями!*/

//Функцияпоследовательнойпередачиданных

voidSCI_send_string(char*string)

{

while(*string)//Длякаждогосимволастроки

{

while(!SCIS1_TDRE);//Ожидание,покабуферпередатчиканеопустеет

SCID=*string;//Записьтекущегосимволавбуферпередатчика

string++;//Увеличиваемномерсимволастроки

}

}

voidmain(void)

{

SOPT1=bBKGDPE;//ВключениелиниифоновойотладкиBKGD

//ПослесбросаBUSCLK=4МГц

SCIBD=26;//СкоростьпередачиSCI=4МГц/(16*26)=9615бит/с

SCIC2=bTE;//Включениепередатчика

SCI_send_string("HelloWorld!");//Передаемданныечерез

//последовательныйинтерфейс

while(1);

}

Рис.11.12. Окно программы HyperTerminal после выполнения программы Примера 11.7.

Изменение полярности сигналов на линии TxD

Интересная особенность модуля SCI в составе HCS08 — возможность изменения полярности сигналов на линии передачи данных TxD. Режим инвертирования сигналов устанавливается битом TXINV в регистре SCIC3. Если бит TXINV = 0, то полярность линии прямая, т.е. старт-бит и нулевые данные соответствуют НИЗКОМУ уровню на линии TxD. Этот режим соответствует установке по умолчанию, также этот режим является типовым для асинхронных приемопередатчиков. Если бит TXINV = 1, то полярность данных на линии TxD инвертируется, т.е. нулевому биту соответствует ВЫСОКОЕ состояние на линии. Описанное свойство доступно только для модулей версий SCIv2, SCIv3 и SCIv4.

Передача сигнала Break

Модуль SCI можно настроить на автоматическую генерацию сообщения «конец сеанса обмена». Этот сигнал представляет собой последовательность из всех нулевых битов, включая стоп-бит. Данная функция включается установкой бита SBK в регистре SCIC2. Модуль SCI генерирует сообщение окончания сеанса обмена, пока бит SBK = 1, и заканчивает генерацию, если бит SBK сбросить в 0.

Длина сообщения определяется значением бита M регистра SCIC1: 8 бит, если M = 0, и 9 бит, если M = 1. В некоторых моделях МК, которые оснащены модулем SCI версий SCIv2, SCIv3 или SCIv4, с помощью бита SCIS2:BRK можно увеличить длину сообщения окончания сеанса обмена на 3 бита. Это означает, что полная длина генерируемого сообщения «конец сеанса обмена» становится равной 13 или 14 бит.

Электронные компоненты Freescale >>>

Подробнее о компании Freescale >>>