11.2. Интерфейс I²C

(Руководство разработчика по микроконтроллерам семейства HCS08)Интерфейс I2C создавался как простой интерфейс с минимально возможным количеством линий связи. Интерфейс I2C использует всего две линии для связи ведущего устройства с ведомым:

- двунаправленная линия данных SDA;

- линия тактирования SCL, которая используется для синхронизации приема и передачи данных.

Связь устройств по интерфейсу I2C на уровне электрических сигналов осуществляется с учетом следующих 4 правил:

- ВЫСОКИЙ уровень на линии данных SDA или на линии тактирования SCL не может быть установлен непосредственно устройством I2C. Все устройства I2C должны иметь выходы с открытым коллектором (или открытым стоком). ВЫСОКИЙ уровень напряжения на линиях формируется внешними подтягивающими резисторами.

- Информация на линии данных SDA считывается только при ВЫСОКОМ уровне на линии тактирования SCL.

- Информация на линию данных SDA выставляется только при НИЗКОМ уровне на линии тактирования SCL.

- Если шина I2C в текущий момент не используется, то на линиях должен быть установлен ВЫСОКИЙ уровень сигнала (логическая 1).

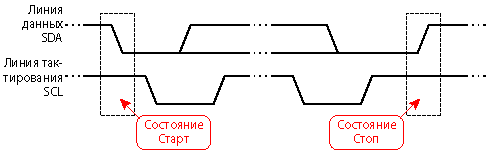

Основной формат кадра обмена по I2C состоит из 11 бит. Сначала следует старт-бит, затем 8 бит данных, далее бит подтверждения приема, затем стоп-бит. Форма представления старт- и стоп-битов нарушает записанное выше правило 3. Старт-бит определяется наличием спадающего фронта на лини SDA при ВЫСОКОМ уровне сигнала на линии SCL. Эту комбинацию сигналов принято также называть стартовым состоянием, или состоянием Старт. Стоп-бит (или состояние Стоп) определяется наличием нарастающего фронта на линии SDA при ВЫСОКОМ уровне на линии SCL. Состояния Старт и Стоп генерируются ведущим устройством (Рис.11.6).

Рис.11.6. Состояния Старт и Стоп на шине I2C.

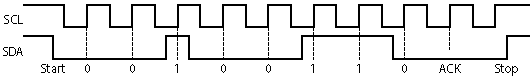

После формирования стартового бита ведущее устройство выставляет на линию данных SDA 8 бит данных, начиная со старшего бита байта. Каждый бит сопровождается импульсом синхронизации SCL. Затем приемник генерирует бит подтверждения приема ACK, устанавливая линию SDA в НИЗКОЕ состояние на интервале девятого импульса на линии SCL.

Если приемник не распознал принятые данные, то он генерирует бит «неподтверждения» приема NACK, просто не переводя линию SDA в НИЗКОЕ состояние. В этом случае передатчик заканчивает текущий сеанс передачи данных и генерирует стоп-бит. В соответствие с алгоритмом прикладной программы передатчик пробует передать информацию позже. На Рис.11.7 показаны временные диаграммы на линиях I2C, которые сопровождают передачу байта 0x26 (передача успешная, бит подтверждения ACK сформирован).

Рис.11.7. Кадр передачи данных по интерфейсу I2C.

Длительность фронтов при переключениях в реальных системах не столь мала, как показано на Рис.11.7, поскольку реальные линии обладают распределенной емкостью и к ним подключены подтягивающие резисторы. Чем выше значения емкости и сопротивления подтягивающих резисторов, тем больше длительности фронтов у сигналов. Большое время нарастания и спада сигнала может привести к ошибкам при обмене данными между устройствами.

При проектировании шины I2C необходимо учитывать количество подключаемых устройств, величину их входной емкости и сопротивлений подтягивающих резисторов. Некоторые производители полупроводниковых приборов предлагают специальные конверторы для увеличения количества подключаемых устройств к шине I2C.

Учтите, что максимальная суммарная емкость подключаемых к линии I2C устройств не должна превышать 400пФ!

Протокол I2C предусматривает возможность принудительного снижения скорости передачи данных ведомым устройством в процессе самой передачи. Когда линия SCL находится в НИЗКОМ состоянии, ведомое устройство может принудительно продлить это состояние на линии, пока оно не будет готово принять следующий бит данных. Данная функция называется «расширением тактовых импульсов».

При необходимости взаимодействия нескольких устройств по шине I2C у каждого подключенного к шине устройства должен быть свой адрес. В соответствии со спецификацией протокола I2C адрес может быть 7- или 10-битным.

На Рис.11.8 представлена структура кадра обмена по I2C при передаче 7-битного адреса. Кадр состоит из старт-бита, 7 бит адреса, бита направления передачи для следующего кадра R/W, бита подтверждения ACK. Первые 9 бит, включая старт-бит, генерируются ведущим устройством, а бит подтверждения приема — ведомым устройством, чей адрес совпадает с адресом, который выставил на линию ведущий.

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | ||

| START | A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W | ACK |

| Адрес ведомого — 7 бит | 1—чтение | 1—ACK | |||||||

Рис.11.8. Формат кадра I2C с передачей адреса ведомого.

Обычно 7-битный адрес состоит из двух частей: первые 4 бит определяют тип ведомого устройства, а последние 3 — номер устройства указанного типа в системе. В Табл.11.4 приведены некоторые типы устройств и их адреса при организации связи по протоколу I2C.

Таблица11.4. Некоторые специальные зарезервированные адреса устройств I2C

| Адрес | Чтение/запись | Описание |

|---|---|---|

| 0000000 | 0 | Адрес общего вызова |

| 0000000 | 1 | Старт-байт (помогаем медленным ведомым устройствам определить начало сеанса передачи данных) |

| 0000001 | x | Адрес CBUS |

| 0000010 | x | Резерв |

| 0000011 | x | Резерв |

| 0000lxx | x | Высокоскоростной ведущий (до 3.4 Мбит/с). Этот режим не реализуется в МК HCS08 |

| 0010xxx | x | Синтезаторы речи |

| 0011xxx | x | Аудиоинтерфейсы PCM |

| 0100xxx | x | Генераторы звуковых частот |

| 0111xxx | x | LED/LCD-дисплеи |

| 1000xxx | x | Видеоинтерфейсы |

| 1001xxx | x | Цифро-аналоговые и аналого-цифровые преобразователи |

| 1010xxx | x | Память |

| 1100xxx | x | ВЧ синтезаторы |

| 1101xxx | x | Часы/календари |

| 11101xx | x | Резерв |

| 11111xx | x | Режим 10-битного адреса |

Бит R/W (чтение/запись), который передается вслед за 7-битным адресом, определяет, что будет происходить с ведомым устройством: данные в него будут записываться (R/W = 0) или считываться из него (R/W = 1).

Процедура адресации происходит следующим образом:

- Ведущее устройство генерирует состояние Старт.

- Ведущее устройство выставляет на линию адрес ведомого устройства.

- Исходя из значения бита R/W, ведущее устройство посылает данные ведомому устройству (если R/W = 0) или считывает данные, выставленные на линию ведомым устройством (R/W = 1).

- Как только все данные посланы, ведущее устройство генерирует на линии состояние Стоп.

В спецификации протокола описан еще один режим, который называется «Повторный старт». В этом режиме ведущее устройство устанавливает еще раз состояние Старт и передает один байт адреса без генерации состояния Стоп. Это бывает полезно для изменения направления передачи данных.

Электронные компоненты Freescale >>>

Подробнее о компании Freescale >>>