# ML7105-002

Bluetooth<sup>®</sup>Low Energy

### Overview

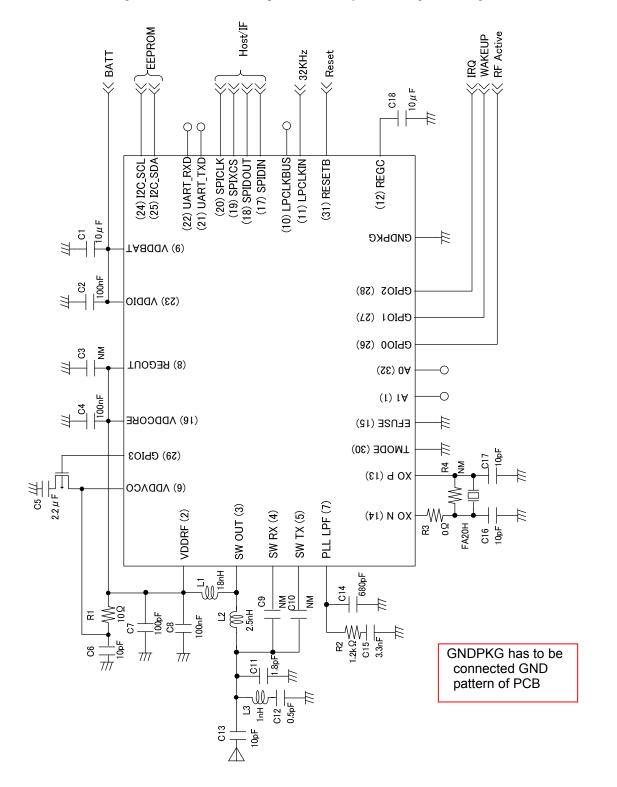

ML7105-002 is a Bluetooth® Low Energy (here in after LE) LSI integrating RF, Baseband, microproccessor core and each peripherals, which has Bluetooth® LE compliant 2.4GHz band radio communication capability. ML7105-002 (hereafter "ML7105") is suitable for applications such as Wrist Watch, Remote Controller or PC peripherals.

### Features

- Bluetooth® SIG Core Spec v4.0 compliant

- Ultra Low Power RF block

- Cortex-M0 Micro processor, it has interrupt controller and Sys-Tick Timer

- 64KB ROM (CODE ROM) for Program, 16KB RAM (DATA RAM) for Data

- 12KB RAM (CODE RAM) for user Program

- Bluetooth<sup>®</sup> LE single mode compliant Baseband controller

- UART interface for Bluetooth<sup>®</sup> Host Controller Interface (HCI)

- SPI (Slave mode) interface for Custom Host Controller Interface

- I2C (Master & Slave) interface for EEPROM or Custom Host Controller Interface

- GPIO ports

- System Clock Timer and External Low Power Clock Timer

- Low Power operating mode

- Single power supply 1.6V to 3.6V

- Operating Temperature -20 deg.C to 70 deg.C

- Current Consumptions Deep Sleep Mode

below 2.9uA (with internal Low Power Clock oscillator circuit)

| Idle Mode |

|-----------|

|           |

| TX mode   |

| RX mode   |

below 3.0mA below 9.0mA below 9.0mA

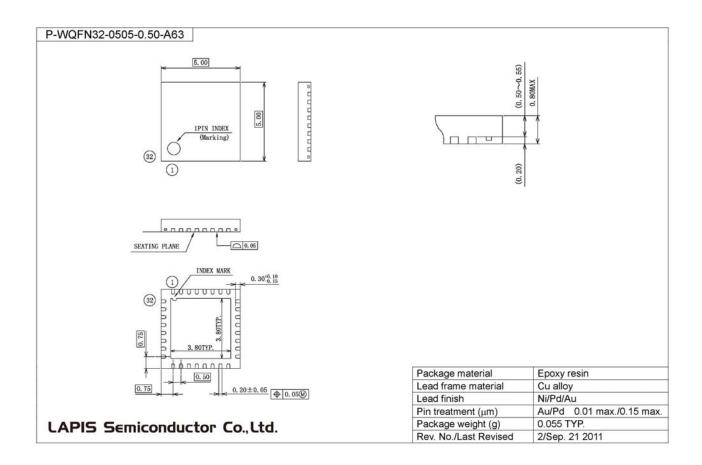

Package

32pins WQFN (P-WQFN32-0505-0.50-A63)

Pb Free, RoHS compliant

#### ML7105-002

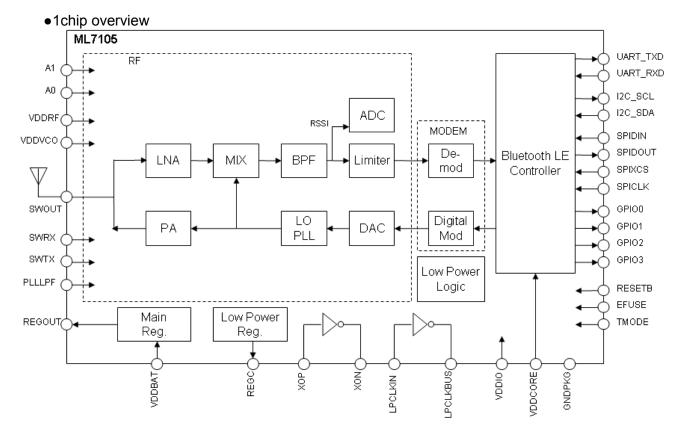

### Block Diagram

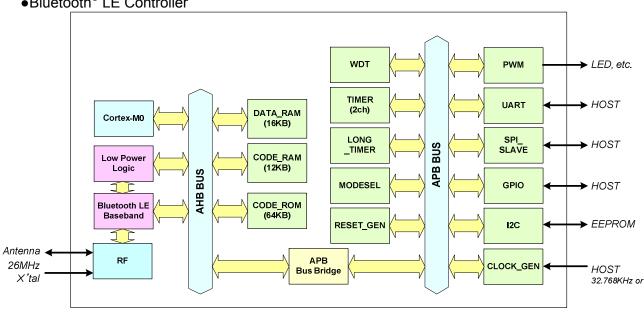

•Bluetooth<sup>®</sup> LE Controller

ML7105-002

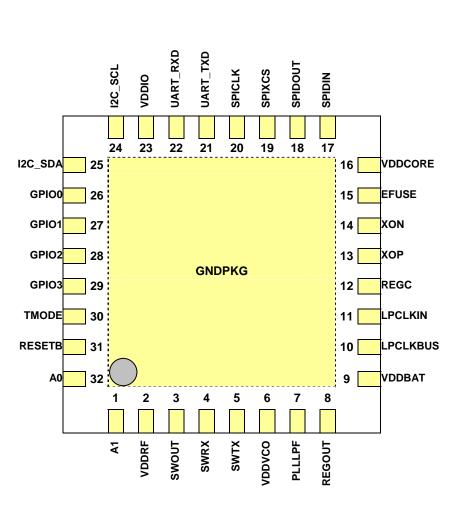

### ■Pin assignment

32pins WQFN

TOP VIEW

Note: Centre of the chip at bottom side is GND (symbol : Package GND)

#### ML7105-002

# ■Pin definitions

| 1     A1     IN     ANA     DIRIO     General purpose analog input       2     VDDRF      PWR     VCC     Power supply for RF block (1 2V)       3     SWOUT     INOUT     ANA     DIRIO_RF     RF signal RX/TX inout       4     SWRX     INOUT     ANA     DIRIO_RF     RX SW control signal       5     SWTX     INOUT     ANA     DIRIO     FR XSW control signal       6     VDDVCO      PWR     VCC     Power supply for RF-VCO (1.2V)       7     PLLLPF     OUT     ANA     DIRIO     Pewer supply for Battery (=VDDIO) (1.6V to 3.6V)       9     VDDBAT      PWR     VCC     Power supply form Battery (=VDDIO) (1.6V to 3.6V)       10     LPCLKBUS     INOUT     ANA     DIRIO     Lew power clock/xtal input       11     LPCLKIN     INOUT     ANA     DIRIO     Decoupling capacitor pin for internal regulator       13     XOP     INOUT     ANA     DIRIO     Power supply for E-Fuse (fixed to GND in normal)       16     VDDCORE      DIG     DIRIO     Power supply for digital core (1.2V)       17     SPIDIN     IN     DIG     CMOS, IN     SPI Slave Data input       18     SPIDOUT     INOUT     DIG                                                                                                          | No. | Pin Name | I/O   | ANA/DIG | IO TYPE   | Function                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|---------|-----------|---------------------------------------------------|

| 3         SWOUT         INOUT         ANA         DIRIO_RF         R signal RXTX inout           4         SWRX         INOUT         ANA         DIRIO_RF         RX SW control signal           5         SWTX         INOUT         ANA         DIRIO_RF         TX SW control signal           6         VDDVCO          PWR         VCC         Power supply for RF-VC0 (1.2V)           7         PILLPF         OUT         ANA         DIRIO         PLL Lops Filter           8         REGOUT         OUT         ANA         DIRIO         PLL Lops Filter           9         VDDBAT          PWR         VCC         Power supply for Battery (=VDDIO) (1.6V to 3.6V)           10         LPCLKBUS         INOUT         ANA         DIRIO         Low power clock output           11         LPCLKIN         INOUT         ANA         DIRIO         Power supply for on internal regulator           12         REGC         OUT         ANA         DIRIO         Power supply for E-Fuse (fixed to GND in normal)           13         XOP         INOUT         ANA         DIRIO         Power supply for digital core (1.2V)           14         XON         INOUT         ANA         DIRO                         | 1   | A1       | IN    | ANA     | DIRIO     | General purpose analog input                      |

| 4         SWRX         INOUT         ANA         DIRIO_RF         RX SW control signal           5         SWTX         INOUT         ANA         DIRIO_RF         TX SW control signal           6         VDDVCO          PWR         VCC         Power supply for RF-VCO (1.2V)           7         PLLLPF         OUT         ANA         DIRIO         PLL cop Filter           8         REGOUT         OUT         ANA         DIRIO         Regulator output           9         VDDBAT          PWR         VCC         Power supply from Battery (=VDDIO) (1.6V to 3.6V)           10         LPCLKBUS         INOUT         ANA         DIRIO         Low power clock output           11         LPCLKIN         INOUT         ANA         DIRIO         Decoupling capacitor pin for internal regulator           12         REGC         OUT         ANA         DIRIO         Positive inout pin for XTAL oscillator block           14         XON         INOUT         ANA         DIRIO         Positive inout pin for XTAL oscillator block           14         XON         INOUT         ANA         DIRIO         Power supply for digital core (1.2V)           17         SPIDN         IN         DIG            | 2   | VDDRF    |       | PWR     | VCC       | Power supply for RF block (1.2V)                  |

| 5         SWTX         INOUT         ANA         DIRIO_RF         TX SW control signal           6         VDDVCO          PWR         VCC         Power supply for RF-VCO (1.2V)           7         PLILEPF         OUT         ANA         DIRIO         PLL Loop Filter           8         REGOUT         OUT         ANA         DIRIO         Regulator output           9         VDDBAT          PWR         VCC         Power supply form Battery (=VDDIO) (1.6V to 3.6V)           10         LPCLKBUS         INOUT         ANA         DIRIO         Low power clock output/           11         LPCLKIN         INOUT         ANA         DIRIO         Decoupling capacitor pin for internal regulator           13         XOP         INOUT         ANA         DIRIO         Positive inout pin for XTAL oscillator block           14         XON         INOUT         ANA         DIRIO         Power supply for digital core (1.2V)           15         EFUSE          DIG         DIRIO         Power supply for digital core (1.2V)           17         SPIDIN         IN         DIG         CMOS, IN         SPI slave Data output           18         SPIDOUT         INOUT         DIG                     | 3   | SWOUT    | INOUT | ANA     | DIRIO_RF  | RF signal RX/TX inout                             |

| 6         VDDVCO          PWR         VCC         Power supply for RF-VCO (1.2V)           7         PLLLPF         OUT         ANA         DIRIO         PLL Loop Filter           8         REGOUT         OUT         ANA         DIRIO         Regulator output           9         VDBAT          PWR         VCC         Power supply from Battery (=VDDIO) (1.6V to 3.6V)           10         LPCLKBUS         INOUT         ANA         DIRIO         Low power clock output/           11         LPCLKIN         INOUT         ANA         DIRIO         Low power clock/Xtal input           12         REGC         OUT         ANA         DIRIO         Decoupling capacitor pin for internal regulator           13         XOP         INOUT         ANA         DIRIO         Negative inout pin for XTAL oscillator block           14         XON         INOUT         ANA         DIRIO         Negative inout pin for XTAL oscillator block           15         EFUSE          PWR         VCC         Power supply for digital core (1.2V)           17         SPIDIN         IN         DIG         CMOS, IN         SPI Slave Data output           18         SPIDOUT         INOUT         DIG               | 4   | SWRX     | INOUT | ANA     | DIRIO_RF  | RX SW control signal                              |

| 7       PLLLPF       OUT       ANA       DIRIO       PLL Loop Filter         8       REGOUT       OUT       ANA       DIRIO       Regulator output         9       VDBBAT        PWR       VCC       Power supply from Battery (=VDDIO) (1.6V to 3.6V)         10       LPCLKBUS       INOUT       ANA       DIRIO       Low power clock output/         11       LPCLKIN       INOUT       ANA       DIRIO       Decoupling capacitor pin for internal regulator         13       XOP       INOUT       ANA       DIRIO       Decoupling capacitor pin for internal regulator         13       XOP       INOUT       ANA       DIRIO       Power supply for Z-Fuse (fixed to GND in normal)         16       VDDCORE        PUR       VCC       Power supply for digital core (1.2V)         17       SPIDIN       IN       DIG       CMOS, IN       SPI Slave Data input         18       SPIDOUT       INOUT       DIG       CMOS, IN       SPI Slave Chip Select         20       SPICLK       IN       DIG       CMOS, IN       SPI Slave Chip Select         20       SPICLK       IN       DIG       CMOS, IN       SPI Slave Chip Select         21       UART_TXD                                                                 | 5   | SWTX     | INOUT | ANA     | DIRIO_RF  | TX SW control signal                              |

| 8         REGOUT         OUT         ANA         DIRIO         Regulator output           9         VDDBAT          PWR         VCC         Power supply from Battery (=VDDIO) (1.6V to 3.6V)           10         LPCLKBUS         INOUT         ANA         DIRIO         Low power clock output/           11         LPCLKIN         INOUT         ANA         DIRIO         Low power clock Attal input           12         REGC         OUT         ANA         DIRIO         Decoupling capacitor pin for internal regulator           13         XOP         INOUT         ANA         DIRIO         Positive inout pin for XTAL oscillator block           14         XON         INOUT         ANA         DIRIO         Power supply for E-Fuse (fixed to GND in normal)           16         VDDCORE          PWR         VCC         Power supply for digital core (1.2V)           17         SPIDIN         IN         DIG         CMOS, IN         SPI slave Data output           18         SPIDOUT         INOUT         DIG         CMOS, IN         SPI slave Chip Select           20         SPICLK         IN         DIG         CMOS, IN         SPI slave Chip Select           21         UART_RXD         IN | 6   | VDDVCO   |       | PWR     | VCC       | Power supply for RF-VCO (1.2V)                    |

| 9         VDDBAT          PWR         VCC         Power supply from Battery (=VDDIO) (1.6V to 3.6V)           10         LPCLKBUS         INOUT         ANA         DIRIO         Low power clock output/           11         LPCLKIN         INOUT         ANA         DIRIO         Low power clock output/           12         REGC         OUT         ANA         DIRIO         Low power clock/Xtal input           12         REGC         OUT         ANA         DIRIO         Decoupling capacitor pin for internal regulator           13         XOP         INOUT         ANA         DIRIO         Positive inout pin for XTAL oscillator block           14         XON         INOUT         ANA         DIRIO         Power supply for E-Fuse (fixed to GND in normal)           16         VDDCORE          PVWR         VCC         Power supply for digital core (1.2V)           17         SPIDIN         IN         DIG         CMOS, IN         SPI slave Data output           18         SPIDOUT         INOUT         DIG         CMOS, IN         SPI slave Clock           21         UART_TXD         OUT         DIG         CMOS, IN         UART TXD output           22         UART_TXD         INOUT | 7   | PLLLPF   | OUT   | ANA     | DIRIO     | PLL Loop Filter                                   |

| 10LPCLKBUSINOUTANADIRIOLow power clock output/11LPCLKININOUTANADIRIOLow power clock output/12REGCOUTANADIRIOLow power clock/Xtal input12REGCOUTANADIRIODecoupling capacitor pin for internal regulator13XOPINOUTANADIRIOPositive inout pin for XTAL oscillator block14XONINOUTANADIRIOPower supply for E-Fuse (fixed to GND in normal)16VDDCOREPWRVCCPower supply for E-Fuse (fixed to GND in normal)16VDDCOREPWRVCCPower supply for digital core (1.2V)17SPIDININDIGCMOS, INSPI Slave Data output18SPIDOUTINOUTDIGCMOS, INSPI Slave Chip Select20SPICLKINDIGCMOS, INSPI Slave Clock21UART_TXDOUTDIGCMOS, INVDAT TXD output22UART_RXDINDIGCMOS, INUART TXD output23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS, BIDIRBIDIR25I2C_SDAINOUTDIGCMOS, BIDIR26GPI00INOUTDIGCMOS, BIDIR27GPI01INOUTDIGCMOS, BIDIR28GPI02INOUTDIGCMOS, BIDIR29(GPI03)                                                                                                                                                                                                                                                                                                                                                               | 8   | REGOUT   | OUT   | ANA     | DIRIO     | Regulator output                                  |

| 11LPCLKININOUTANADIRIOLow power clock/Xtal input12REGCOUTANADIRIODecoupling capacitor pin for internal regulator13XOPINOUTANADIRIOPositive inout pin for XTAL oscillator block14XONINOUTANADIRIOPositive inout pin for XTAL oscillator block15EFUSEDIGDIRIOPower supply for E-Fuse (fixed to GND in normal)16VDDCOREPWRVCCPower supply for E-Fuse (fixed to GND in normal)16VDDCOREPWRVCCPower supply for digital core (1.2V)17SPIDININDIGCMOS, INSPI slave Data input18SPIDOUTINOUTDIGCMOS, INSPI slave Data output19SPIXCSINDIGCMOS, INSPI slave Clock21UART_TXDOUTDIGCMOS, INSPI slave Clock21UART_RXDINDIGCMOS, INUART TXD output22UART_RXDINDIGCMOS, BIDIRI2C_SCL23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS, BIDIRI2C_SCL25I2C_SDAINOUTDIGCMOS, BIDIRGPIO inout/RF_ACTIVE26GPI00INOUTDIGCMOS, BIDIRGPIO inout/RQ27GPI03INOUTDIGCMOS, BIDIRGPIO inout/RQ29(PIO3<                                                                                                                                                                                                                                                                                                                                     | 9   | VDDBAT   |       | PWR     | VCC       | Power supply from Battery (=VDDIO) (1.6V to 3.6V) |

| 12REGCOUTANADIRIODecoupling capacitor pin for internal regulator13XOPINOUTANADIRIOPositive inout pin for XTAL oscillator block14XONINOUTANADIRIONegative inout pin for XTAL oscillator block15EFUSEDIGDIRIOPower supply for E-Fuse (fixed to GND in normal)16VDDCOREPWRVCCPower supply for digital core (1.2V)17SPIDININDIGCMOS, INSPI Slave Data input18SPIDOUTINOUTDIGCMOS, INSPI Slave Data output19SPIXCSINDIGCMOS, INSPI Slave Chip Select20SPICLKINDIGCMOS, INSPI Slave Clock21UART_TXDOUTDIGCMOS, INSPI Slave Clock22UART_RXDINDIGCMOS, INUART TXD output23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS, BIDIRI2C_SCL25I2C_SDAINOUTDIGCMOS, BIDIRGPIO inout/RF_ACTIVE26GPIO0<br>(RF_ACTIVEINOUTDIGCMOS, BIDIRGPIO inout/RQ28GPIO2<br>(IRQINOUTDIGCMOS, BIDIRGPIO inout/IRQ29(PS_CONTROLINOUTDIGCMOS, INTESTMODE input30TMODEINDIGCMOS, INReset input31RESETBIN                                                                                                                                                                                                                                                                                                                                        | 10  | LPCLKBUS | INOUT | ANA     | DIRIO     | Low power clock output/                           |

| 13         XOP         INOUT         ANA         DIRIO         Positive inout pin for XTAL oscillator block           14         XON         INOUT         ANA         DIRIO         Negative inout pin for XTAL oscillator block           15         EFUSE          DIG         DIRIO         Power supply for E-Fuse (fixed to GND in normal)           16         VDDCORE          PWR         VCC         Power supply for digital core (1.2V)           17         SPIDIN         IN         DIG         CMOS, IN         SPI Slave Data input           18         SPIDOUT         INOUT         DIG         CMOS, IN         SPI Slave Data output           19         SPIXCS         IN         DIG         CMOS, IN         SPI Slave Chip Select           20         SPICLK         IN         DIG         CMOS, IN         SPI Slave Chip Select           21         UART_TXD         OUT         DIG         CMOS, IN         VART TXD output           22         UART_RXD         IN         DIG         CMOS, IN         VART TXD output           23         VDDIO          PWR         VCC         Power supply for digital IO (1.6V to 3.6V)           24         I2C_SCL         INOUT         DIG                  | 11  | LPCLKIN  | INOUT | ANA     | DIRIO     | Low power clock/Xtal input                        |

| 14XONINOUTANADIRIONegative inout pin for XTAL oscillator block15EFUSEDIGDIRIOPower supply for E-Fuse (fixed to GND in normal)16VDDCOREPWRVCCPower supply for digital core (1.2V)17SPIDININDIGCMOS, INSPI Slave Data input18SPIDOUTINOUTDIGCMOS, BiDIRSPI Slave Data output19SPIXCSINDIGCMOS, INSPI Slave Chip Select20SPICLKINDIGCMOS, OUT UART TXD output21UART_TXDOUTDIGCMOS, INVART TXD output22UART_RXDINDIGCMOS, INUART TXD output23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS, BIDIRBIDIR25I2C_SDAINOUTDIGCMOS, BIDIRGPIO inout/RF_ACTIVE26GPI00INOUTDIGCMOS, BIDIRGPIO inout/RF_ACTIVE27GPI01INOUTDIGCMOS, BIDIRGPIO inout/WAKEUP28GPI02INOUTDIGCMOS, BIDIRGPIO inout/IRQ29GFI03INOUTDIGCMOS, BIDIRGPIO inout/IRQ30TMODEINDIGCMOS, BIDIRGPIO inout/external control switch control30TMODEINDIGCMOS, INReset input31RESETBINDIGCMOS, INReset                                                                                                                                                                                                                                                                                                                                                         | 12  | REGC     | OUT   | ANA     | DIRIO     | Decoupling capacitor pin for internal regulator   |

| 15EFUSEDIGDIRIOPower supply for E-Fuse (fixed to GND in normal)16VDDCOREPWRVCCPower supply for digital core (1.2V)17SPIDININDIGCMOS, INSPI Slave Data input18SPIDOUTINOUTDIGCMOS, INSPI Slave Data output19SPIXCSINDIGCMOS, INSPI Slave Data output20SPICLKINDIGCMOS, INSPI Slave Chip Select21UART_TXDOUTDIGCMOS, INSPI Slave Clock22UART_RXDINDIGCMOS, INUART TXD output23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS, BIDIR<br>BIDIRI2C_SCL25I2C_SDAINOUTDIGCMOS, BIDIR<br>BIDIRGPIO inout/RF_ACTIVE26GPI00<br>/(RF_ACTIVEINOUTDIGCMOS, BIDIR<br>BIDIRGPIO inout/RF_ACTIVE28GPI02<br>/(RQINOUTDIGCMOS, BIDIR<br>BIDIRGPIO inout/REQ29GPI03<br>/(PS_CONTROLINOUTDIGCMOS, IN<br>BIDIRGPIO inout/RCQ30TMODEINDIGCMOS, IN<br>BIDIRGPIO inout/external control switch control31RESETBINDIGCMOS, IN<br>BIDIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                       | 13  | XOP      | INOUT | ANA     | DIRIO     | Positive inout pin for XTAL oscillator block      |

| 16VDDCOREPWRVCCPower supply for digital core (1.2V)17SPIDININDIGCMOS, INSPI Slave Data input18SPIDOUTINOUTDIGCMOS, BiDIRSPI Slave Data output19SPIXCSINDIGCMOS, INSPI Slave Chip Select20SPICLKINDIGCMOS, INSPI Slave Clock21UART_TXDOUTDIGCMOS, INSPI Slave Clock22UART_RXDINDIGCMOS, INUART TXD output23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS, BiDIR<br>BiDIRI2C_SCL25I2C_SDAINOUTDIGCMOS, BiDIR<br>BiDIRGPIO inout/RF_ACTIVE26GPI00<br>(RF_ACTIVEINOUTDIGCMOS, BiDIR<br>BiDIRGPIO inout/RF_ACTIVE27GPI01<br>(NAKEUPINOUTDIGCMOS, BIDIR<br>BIDIRGPIO inout/RF_ACTIVE28GPI02<br>(RFQINOUTDIGCMOS, BIDIR<br>BIDIRGPIO inout/RCQ29GPI03<br>(/PS_CONTROLINOUTDIGCMOS, IN<br>BIDIRGPIO inout/external control switch control30TMODEINDIGCMOS, IN<br>BIDIRGPIO inout/external control switch control31RESETBINDIGCMOS, IN<br>BIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                            | 14  | XON      | INOUT | ANA     | DIRIO     | Negative inout pin for XTAL oscillator block      |

| 17SPIDININDIGCMOS, INSPI Slave Data input18SPIDOUTINOUTDIGCMOS, BiDIRSPI Slave Data output19SPIXCSINDIGCMOS, INSPI Slave Chip Select20SPICLKINDIGCMOS, INSPI Slave Clock21UART_TXDOUTDIGCMOS, OUTUART TXD output22UART_RXDINDIGCMOS, INVART RXD input23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS, BiDIRI2C_SCL25I2C_SDAINOUTDIGCMOS, BiDIRI2C_SDA26GPIO0INOUTDIGCMOS, BiDIRGPIO inout/RF_ACTIVE27GPIO1INOUTDIGCMOS, BiDIRGPIO inout/RF_ACTIVE28GPIO2INOUTDIGCMOS, BiDIRGPIO inout/WAKEUP29GPIO3INOUTDIGCMOS, BiDIRGPIO inout/RQ30TMODEINDIGCMOS, BIDIRGPIO inout/external control switch control30TMODEINDIGCMOS, INReset input31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15  | EFUSE    |       | DIG     | DIRIO     | Power supply for E-Fuse (fixed to GND in normal)  |

| 18SPIDOUTINOUTDIGCMOS,<br>BiDIRSPI Slave Data output19SPIXCSINDIGCMOS, INSPI Slave Chip Select20SPICLKINDIGCMOS, INSPI Slave Clock21UART_TXDOUTDIGCMOS, OUTUART TXD output22UART_RXDINDIGCMOS, OUTUART TXD output23VDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS,<br>BiDIRI2C_SCL25I2C_SDAINOUTDIGCMOS,<br>BiDIRI2C_SDA26GPIO0<br>/RF_ACTIVEINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE27GPIO1<br>/WAKEUPINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE28GPIO2<br>/IRQINOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ29GPIO3<br>/PS_CONTROLINOUTDIGCMOS,<br>BIDIRGPIO inout/IRQ30TMODEINDIGCMOS, INTESTMODE input31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16  | VDDCORE  |       | PWR     | VCC       | Power supply for digital core (1.2V)              |

| 18SPIDOUIINOUIDIGBIDIRSPI Slave Data output19SPIXCSINDIGCMOS, INSPI Slave Chip Select20SPICLKINDIGCMOS, INSPI Slave Clock21UART_TXDOUTDIGCMOS, OUTUART TXD output22UART_RXDINDIGCMOS, INUART RXD input23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS, BIDIRI2C_SCL25I2C_SDAINOUTDIGCMOS, BIDIRI2C_SDA26GPIO0<br>(RF_ACTIVEINOUTDIGCMOS, BIDIRGPIO inout/RF_ACTIVE27GPI01<br>(MAKEUPINOUTDIGCMOS, BIDIRGPIO inout/RF_ACTIVE28GPIO2<br>(JRQINOUTDIGCMOS, BIDIRGPIO inout/IRQ29GPI03<br>(PS_CONTROLINOUTDIGCMOS, BIDIRGPIO inout/IRQ30TMODEINDIGCMOS, BIDIRGPIO inout/IRQ31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17  | SPIDIN   | IN    | DIG     | CMOS, IN  | SPI Slave Data input                              |

| 20SPICLKINDIGCMOS, INSPI Slave Clock21UART_TXDOUTDIGCMOS, OUTUART TXD output22UART_RXDINDIGCMOS, INUART RXD input23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS, BiDIRI2C_SCL25I2C_SDAINOUTDIGCMOS, BiDIRI2C_SDA26GPIO0INOUTDIGCMOS, BiDIRGPIO inout/RF_ACTIVE27GPIO1INOUTDIGCMOS, BiDIRGPIO inout/RF_ACTIVE28GPIO2INOUTDIGCMOS, BiDIRGPIO inout/IRQ29GPIO3INOUTDIGCMOS, BIDIRGPIO inout/IRQ30TMODEINDIGCMOS, INTESTMODE input31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18  | SPIDOUT  | INOUT | DIG     | -         | SPI Slave Data output                             |

| 21UART_TXDOUTDIGCMOS, OUTUART TXD output22UART_RXDINDIGCMOS, INUART RXD input23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS,<br>BiDIRI2C_SCL25I2C_SDAINOUTDIGCMOS,<br>BiDIRI2C_SDA26GPIO0<br>(RF_ACTIVEINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE27GPIO1<br>(WAKEUPINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE28GPIO2<br>(IRQINOUTDIGCMOS,<br>BiDIRGPIO inout/RQ29GPIO3<br>(PS_CONTROLINOUTDIGCMOS,<br>BiDIRGPIO inout/RQ30TMODEINDIGCMOS, INTESTMODE input31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19  | SPIXCS   | IN    | DIG     | CMOS, IN  | SPI Slave Chip Select                             |

| 22UART_RXDINDIGCMOS, INUART RXD input23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS,<br>BiDIRI2C_SCL25I2C_SDAINOUTDIGCMOS,<br>BiDIRI2C_SDA26GPIO0<br>(/RF_ACTIVEINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE27GPIO1<br>/WAKEUPINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE28GPIO2<br>/IRQINOUTDIGCMOS,<br>BiDIRGPIO inout/RRQ29GPIO3<br>/IRQINOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ30TMODEINDIGCMOS, BIDIR31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20  | SPICLK   | IN    | DIG     | CMOS, IN  | SPI Slave Clock                                   |

| 23VDDIOPWRVCCPower supply for digital IO (1.6V to 3.6V)24I2C_SCLINOUTDIGCMOS,<br>BiDIRI2C_SCL25I2C_SDAINOUTDIGCMOS,<br>BiDIRI2C_SDA26GPIO0<br>/RF_ACTIVEINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE27GPIO1<br>/WAKEUPINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE28GPIO2<br>/IRQINOUTDIGCMOS,<br>BiDIRGPIO inout/RQ29GPIO3<br>/PS_CONTROLINOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ30TMODEINDIGCMOS, BIDIRGPIO inout/external control switch control31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21  | UART_TXD | OUT   | DIG     | CMOS, OUT | UART TXD output                                   |

| 24I2C_SCLINOUTDIGCMOS,<br>BiDIRI2C_SCL25I2C_SDAINOUTDIGCMOS,<br>BiDIRI2C_SDA26GPIO0<br>/RF_ACTIVEINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE27GPIO1<br>/WAKEUPINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE28GPIO2<br>/IRQINOUTDIGCMOS,<br>BiDIRGPIO inout/WAKEUP29GPIO3<br>/PS_CONTROLINOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ30TMODEINDIGCMOS, INTESTMODE input31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22  | UART_RXD | IN    | DIG     | CMOS, IN  | UART RXD input                                    |

| 24I2C_SCLINOUTDIGBiDIRI2C_SCL25I2C_SDAINOUTDIGCMOS,<br>BiDIRI2C_SDA26GPIO0<br>/RF_ACTIVEINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE27GPIO1<br>/WAKEUPINOUTDIGCMOS,<br>BiDIRGPIO inout/WAKEUP28GPIO2<br>/IRQINOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ29GPIO3<br>/PS_CONTROLINOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ30TMODEINDIGCMOS, INTESTMODE input31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23  | VDDIO    |       | PWR     | VCC       | Power supply for digital IO (1.6V to 3.6V)        |

| 25I2C_SDAINOUTDIGBiDIRI2C_SDA26GPIO0<br>/RF_ACTIVEINOUTDIGCMOS,<br>BiDIRGPIO inout/RF_ACTIVE27GPIO1<br>/WAKEUPINOUTDIGCMOS,<br>BiDIRGPIO inout/WAKEUP28GPIO2<br>/IRQINOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ29GPIO3<br>/PS_CONTROLINOUTDIGCMOS,<br>BiDIRGPIO inout/external control switch control30TMODEINDIGCMOS, INTESTMODE input31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24  | I2C_SCL  | INOUT | DIG     |           | I2C_SCL                                           |

| 26/RF_ACTIVEINOUTDIGBiDIRGPIO inout/RF_ACTIVE27GPIO1INOUTDIGCMOS,<br>BiDIRGPIO inout/WAKEUP28GPIO2<br>/IRQINOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ29GPIO3<br>/PS_CONTROLINOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ30TMODEINDIGCMOS, INGPIO inout/external control switch control31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25  | I2C_SDA  | INOUT | DIG     | -         | I2C_SDA                                           |

| 27/WAKEUPINOUTDIGBiDIRGPIO inout/WAKEUP28GPIO2INOUTDIGCMOS,<br>BiDIRGPIO inout/IRQ29GPIO3INOUTDIGCMOS,<br>BiDIRGPIO inout/external control switch control30TMODEINDIGCMOS, INGPIO inout/external control switch control31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26  |          | INOUT | DIG     |           | GPIO inout/RF_ACTIVE                              |

| 28/IRQINOUTDIGBiDIRGPIO Inout/IRQ29GPIO3INOUTDIGCMOS,<br>BiDIRGPIO inout/external control switch control30TMODEINDIGCMOS, INTESTMODE input31RESETBINDIGCMOS, INReset input32A0INANADIRIOGeneral purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27  |          | INOUT | DIG     |           | GPIO inout/WAKEUP                                 |

| 29     /PS_CONTROL     INOUT     DIG     BiDIR     GPIO inout/external control switch control       30     TMODE     IN     DIG     CMOS, IN     TESTMODE input       31     RESETB     IN     DIG     CMOS, IN     Reset input       32     A0     IN     ANA     DIRIO     General purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28  |          | INOUT | DIG     |           | GPIO inout/IRQ                                    |

| 30     TMODE     IN     DIG     CMOS, IN     TESTMODE input       31     RESETB     IN     DIG     CMOS, IN     Reset input       32     A0     IN     ANA     DIRIO     General purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29  |          | INOUT | DIG     |           | GPIO inout/external control switch control        |

| 32 A0 IN ANA DIRIO General purpose analog input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30  | TMODE    | IN    | DIG     | CMOS, IN  | TESTMODE input                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31  | RESETB   | IN    | DIG     | CMOS, IN  | Reset input                                       |

| G GNDPKG GND GND Package GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32  | A0       | IN    | ANA     | DIRIO     | General purpose analog input                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | G   | GNDPKG   |       | GND     | GND       | Package GND                                       |

#### ML7105-002

### ■Pin definition

| 1/0         |                 |   | DE innut and autout                     |

|-------------|-----------------|---|-----------------------------------------|

| I/O         | I <sub>RF</sub> |   | RF input and output                     |

| definitions | I               | : | Digital input                           |

|             | lpd             | : | Digital input with pull-down resistor   |

|             | IA              | : | Analog input                            |

|             | I <sub>AH</sub> | : | Analog input support 3V                 |

|             | I <sub>SH</sub> | : | Low-Power Clock input                   |

|             | X <sub>SH</sub> | : | X'tal pin for Low-Power Clock           |

|             | XM              | : | X'tal pin for Master Clock              |

|             | O <sub>2</sub>  | : | Digital output with 2mA load capability |

|             | B2              | : | Digital inout with 2mA load capability  |

|             | OA              | : | Analog output                           |

|             | OAH             | : | Analog output support 3V                |

### •RF analog pins

| No | Pin Name | Status in<br>reset | I/O              | Active<br>Level | Function                     |

|----|----------|--------------------|------------------|-----------------|------------------------------|

| 3  | SWOUT    | Hi-Z               | I <sub>RF</sub>  |                 | RF signal RX/TX inout        |

| 4  | SWRX     | Hi-Z               | I <sub>RF</sub>  |                 | RX SW control signal         |

| 5  | SWTX     | Hi-Z               | I <sub>RF</sub>  |                 | TX SW control signal         |

| 32 | A0       | Hi-Z               | I <sub>AH</sub>  |                 | General purpose analog input |

| 1  | A1       | Hi-Z               | I <sub>AH,</sub> |                 | General purpose analog input |

| 7  | PLLLPF   | Hi-Z               | O <sub>A</sub>   |                 | PLL Loop Filter              |

### •XO, LPXO pins

| No | Pin Name | Status in reset | I/O              | Active<br>Level | Function                                             |

|----|----------|-----------------|------------------|-----------------|------------------------------------------------------|

| 13 | XOP      | Hi-Z            | X <sub>M</sub>   |                 | Positive inout pin for Master clock oscillator block |

| 14 | XON      | Hi-Z            | X <sub>M</sub>   |                 | Negative inout pin for Master clock oscillator block |

| 10 | LPCLKBUS | 0V              | X <sub>SH</sub>  |                 | Low power clock Xtal output                          |

| 11 | LPCLKIN  | I <sub>SH</sub> | $X_{SH}, I_{SH}$ |                 | Low power clock/Xtal input                           |

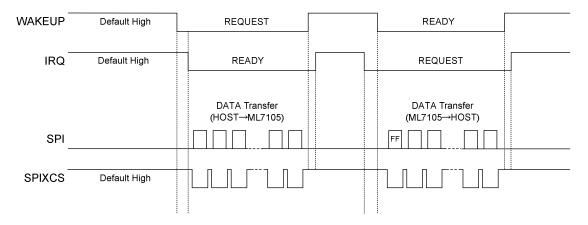

### •SPI pins

| No | Pin Name | Status in<br>reset | I/O | Active<br>Level | Function              |

|----|----------|--------------------|-----|-----------------|-----------------------|

| 17 | SPIDIN   | Input              | I   |                 | SPI SLAVE Data input  |

| 18 | SPIDOUT  | Output             | B2  |                 | SPI SLAVE Data output |

| 19 | SPIXCS   | Input              | I   | Low             | SPI SLAVE Chip Select |

| 20 | SPICLK   | Input              | Ι   |                 | SPI SLAVE Clock       |

#### ML7105-002

### •UART pins

| No | Pin Name | Status in<br>reset | I/O            | Active<br>Level | Function        |

|----|----------|--------------------|----------------|-----------------|-----------------|

| 21 | UART_TXD | High output        | O <sub>2</sub> |                 | UART TXD output |

| 22 | UART_RXD | input              | lpd            |                 | UART RXD input  |

### •I2C pins

| No | Pin Name | Status in<br>reset | I/O | Active<br>Level | Function |

|----|----------|--------------------|-----|-----------------|----------|

| 24 | I2C_SCL  | Input              | B2  |                 | I2C_SCL  |

| 25 | I2C_SDA  | Input              | B2  |                 | I2C_SDA  |

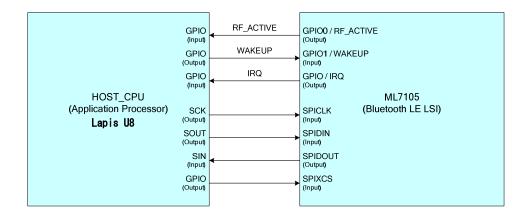

### •GPIO pins

| No | Pin Name             | Status in<br>reset | I/O | Active<br>Level | Function                                                     |

|----|----------------------|--------------------|-----|-----------------|--------------------------------------------------------------|

| 26 | GPIO0<br>/RF_ACTIVE  | Low output         | B2  |                 | GPIO inout/RF_ACTIVE (default : RF_ACTIVE)                   |

| 27 | GPIO1<br>/WAKEUP     | Input              | B2  |                 | GPIO inout/WAKEUP (default : WAKEUP)                         |

| 28 | GPIO2<br>/IRQ        | High output        | B2  |                 | GPIO inout/IRQ (default : IRQ)                               |

| 29 | GPIO3<br>/PS_CONTROL | Low output         | B2  |                 | GPIO inout/external switch control<br>(default : PS_CONTROL) |

#### •Miscellaneous pins

| No | Pin Name | Status in<br>reset | I/O | Active<br>Level | Function                                         |

|----|----------|--------------------|-----|-----------------|--------------------------------------------------|

| 31 | RESETB   | input              | I   | Low             | Reset input (Low = Reset)                        |

| 15 | EFUSE    |                    |     |                 | Power supply for E-Fuse (fixed to GND in normal) |

| 30 | TMODE    | input              | Ι   |                 | TESTMODE input (Low = normal mode)               |

### •Regulator pins

| No | Pin Name | Status in<br>reset | I/O             | Active<br>Level | Function                                        |

|----|----------|--------------------|-----------------|-----------------|-------------------------------------------------|

| 8  | REGOUT   | Hi-Z               | O <sub>AH</sub> |                 | Regulator output                                |

| 12 | REGC     | 1.2V output        | O <sub>AH</sub> |                 | Decoupling capacitor pin for internal regulator |

#### ML7105-002

#### •Power Supply pin

| No | Pin Name | Status in<br>reset | I/O | Active<br>Level | Function                                          |

|----|----------|--------------------|-----|-----------------|---------------------------------------------------|

| 2  | VDDRF    |                    |     |                 | Power supply for RF block (1.2V)                  |

| 6  | VDDVCO   |                    |     |                 | Power supply for RF-VCO (1.2V)                    |

| 9  | VDDBAT   |                    |     |                 | Power supply from Battery (=VDDIO) (1.6V to 3.6V) |

| 16 | VDDCORE  |                    |     |                 | Power supply for digital core (1.2V)              |

| 23 | VDDIO    |                    |     |                 | Power supply for digital IO (1.6V to 3.6V)        |

| G  | GNDPKG   |                    |     |                 | Package GND                                       |

#### •Unused pins

Followings are recommendation for pins are not used.

| No | Pin Name | Recommendation                                      |

|----|----------|-----------------------------------------------------|

| 1  | A1       | Open                                                |

| 10 | LPCLKBUS | Open                                                |

| 15 | EFUSE    | Fix to GND                                          |

| 17 | SPIDIN   | Fix to VDDIO                                        |

| 18 | SPIDOUT  | Fix to VDDIO                                        |

| 19 | SPIXCS   | Fix to VDDIO                                        |

| 20 | SPICLK   | Fix to VDDIO                                        |

| 21 | UART_TXD | Open                                                |

| 22 | UART_RXD | Fix to GND (See operating mode section)             |

| 24 | I2C_SCL  | Fix to VDDIO                                        |

| 25 | I2C_SDA  | Fix to GND                                          |

| 26 | GPIO0    | Open                                                |

| 27 | GPIO1    | Fix to VDDIO or GND<br>(See operating mode section) |

| 28 | GPIO2    | Open                                                |

| 29 | GPIO3    | Open                                                |

| 32 | A0       | Open                                                |

#### Note

Leaving input pins open with Hi-Z status, current consumption will be increased. It is highly recommended that input or inout pins should not be left open.

### Electrical Characteristics

### •Absolute Maximum Rating

| Item                        | Symbol           | Condition             | Rating            | Unit  |

|-----------------------------|------------------|-----------------------|-------------------|-------|

| Power supply 3.3V (*1)      | Vddio1<br>Vddio2 |                       | -0.3 to +4.6      | V     |

| Power supply 1.2V (*2)      | VDDRF            |                       | -0.3 to +1.8      | V     |

| Digital input voltage (*4)  | Vdin             |                       | -0.3 to VDDIO+0.3 | V     |

| Digital output voltage (*5) | Vdo              | Ta = -20 to +70 deg.C | -0.3 to VDDIO+0.3 | V     |

| Analog IO voltage (*6)      | VA               | GND= 0 V (*3)         | -0.3 to VDDRF+0.3 | V     |

| Analog HV IO voltage (*7)   | Vah              | VDDRF=VDDVCO          | -0.3 to VDDIO+0.3 | V     |

| Digital IO load current     | Ido              | =VDDCORE,             | -10 to +10        | mA    |

| Analog IO current (*6)(*7)  | la               | VDDBAT=VDDIO,         | –2 to +2          | mA    |

| Power Dissipation           | PD               |                       | 1.0               | W     |

| Storage temperature         | Tstg             | _                     | –55 to +125       | deg.C |

(\*1) VDDBAT, VDDIO pins (\*2) VDDRF, VDDVCO, VDDCORE,

(\*3) GND: GND pin (Package GND) (\*4) IO pins with I, IPD, B2 symbol in pin definition

(\*5) IO pins with  $O_2, B_2$  symbol in pin definition

(\*6) IO pins with IA, OA,  $X_M$  symbol in pin definition

(\*7) IO pins with IAH, OAH,  $I_{SH}$ ,  $X_{SH}$ , symbol in pin definition

#### Recommended Operating Conditions

| Item                                                            | Symbol           | Condition                                                        | Min         | Тур    | Max         | Unit |

|-----------------------------------------------------------------|------------------|------------------------------------------------------------------|-------------|--------|-------------|------|

| Power Supply                                                    | VDDIO1           | VDDIO pin<br>(VDDBAT≧VDDIO)                                      | 1.6         | 3.3    | 3.6         | V    |

| Power Supply                                                    | Vddio2           | VDDBAT pin<br>(VDDBAT≧VDDIO)                                     | 1.6         | 3.3    | 3.6         | V    |

| Ambient Temperature                                             | Ta               | _                                                                | -20         | +25    | +85         | °C   |

| Rising time digital input pins                                  | t <sub>IR1</sub> | Digital input/inout pins                                         | _           | _      | 20          | Ns   |

| Falling time digital input pins                                 | t <sub>IF1</sub> | Digital input/inout pins                                         | _           | _      | 20          | Ns   |

| Load capacitance digital                                        | Cdl              | Digital output/inout pins                                        | _           | _      | 20          | pF   |

| Master Clock (26 MHz)<br>crystal oscillator frequency           | FMCK1            | Connect cristal oscillator<br>between XOP-XON pins<br>(*1), (*2) | –40<br>ppm  | 26     | +40<br>ppm  | MHz  |

| Low Power Clock<br>(32.768 kHz)<br>crystal oscillator frequency | FLPCK1           | LPCLKIN pin,<br>LPCLKBUS pin (*2)                                | –250<br>ppm | 32.768 | +250<br>ppm | kHz  |

| Low Power Clock<br>Input Duty Ratio                             | DLPCK1           | External input from LPCLKIN, LPCLKBUS pin left OPEN              | 30          | 50     | 70          | %    |

| RF Channel frequency (*2)                                       | Frf              | SWOUT pin                                                        | 2402        | _      | 2480        | MHz  |

| RF input level                                                  | Prfin            |                                                                  | -70         | -      | -10         | dBm  |

(\*1) Cristal oscillator is recommended

(\*2) The cristal should be used the one that meet the specification include peripheral circuit.

(\*3) Frequency range F = 2402 + 2 x k [MHz] here k=0, 1,2,...,39.

#### ML7105-002

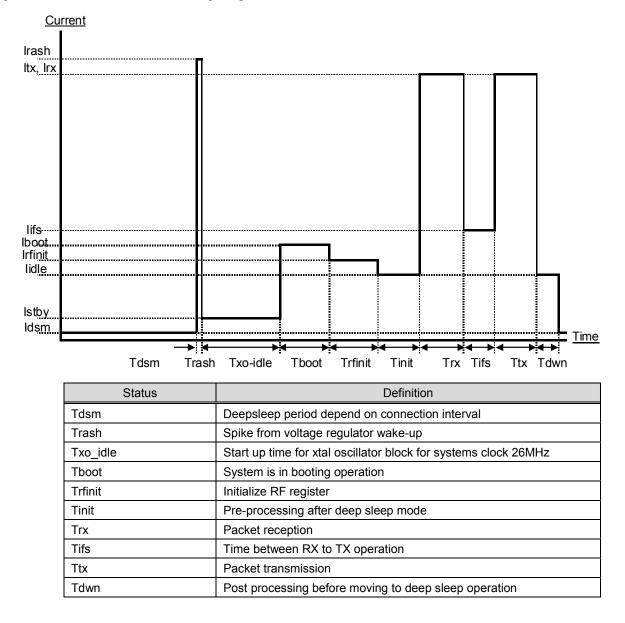

#### •Current consumption

(Ta = -20 to +70 deg.C)

| Item                | Symbol | Condition                                                  | Min | Тур  | Max | Unit |

|---------------------|--------|------------------------------------------------------------|-----|------|-----|------|

|                     | IDD1   | Deep Sleep state (External Low<br>Power Clock)             | -   | 0.7  | -   | uA   |

|                     | Idd2   | Deep Sleep state (Internal Low<br>Power Clock oscillation) | -   | 2.9  | Ι   | uA   |

| Current Consumption | Idd3   | Idle state                                                 | _   | 3    | -   | mA   |

| (*1)                | IDD4   | RF RX state                                                |     | 9    | -   | mA   |

|                     | loor   | RF TX state<br>(-6dBm)                                     | _   | 9    | _   | mA   |

|                     | IDD5   | RF TX state<br>(0dBm)                                      | _   | 10.9 | -   | mA   |

(\*1) Condition: Ta = 25deg. VDDHV = 3.3V

#### •DC characteristics

|                                      |        |                                                      |               | (Ta = | -20 to +7     | 0 deg.C) |

|--------------------------------------|--------|------------------------------------------------------|---------------|-------|---------------|----------|

| Item                                 | Symbol | Condition                                            | Min           | Тур   | Max           | Unit     |

| H level Voltage Input                | VIH1   | (*1) (*2) (*5)                                       | Vddio<br>X0.7 | Ι     | Vddio         | V        |

| L level Voltage input                | VIL1   | (*1) (*2) (*5)                                       | 0             | -     | VDDIO<br>X0.3 | V        |

| LPCLKIN pin<br>H level Voltage Input | VIH2   | (*3)                                                 | 1             | Ι     | VDDIO         | V        |

| LPCLKIN pin<br>L level Voltage input | VIL2   | (*3)                                                 | 0             | Ι     | 0.3           | V        |

|                                      | IIH1   | VIH = VDDIO (*1) (*5)                                | -1            | -     | 1             | uA       |

| Input leak current                   | Іін2   | VIH = VDDIO (*2)                                     | 5             | -     | 250           | uA       |

|                                      | lı∟1   | VIL = 0 V (*1) (*2) (*5)                             | 1             | -     | 1             | uA       |

| Tri-state output leak                | lozн   | Voh = Vddio (*4) (*5)                                | -1            | -     | 1             | uA       |

| current                              | Iozl   | Vol = 0 V (*4) (*5)                                  | -1            | I     | 1             | uA       |

| H level Voltage Output               | Vон    | Iон = -2mA (*4) (*5)<br>Vddio = VddrF = 1.6V to 3.6V | VDDIO × 0.75  | Ι     | Vddio         | V        |

| L level Voltage Output               | Vol    | IoL = 2mA (*4) (*5)                                  | 0             | _     | VDDIO × 0.25  | V        |

| Input pin capacitance                | CIN    | F=1MHz (*1) (*2) (*4) (*5)                           | -             | 8     | _             | pF       |

(\*1) IO pins with I symbol in pin definition

(\*2) IO pins with IPD symbol in pin definition

(\*3) IO pins with ISH symbol in pin definition

(\*4) IO pins with O2 symbol in pin definition

(\*5) IO pins with B2 symbol in pin definition

#### ML7105-002

### •RF Characteristics

|                                                |                     |                                                                          |      |      | Га = –20 t | 1    |

|------------------------------------------------|---------------------|--------------------------------------------------------------------------|------|------|------------|------|

| Item                                           | Symbol              | Condition                                                                | Min  | Тур  | Max        | Unit |

| ТХ                                             | r –                 |                                                                          |      | 1    | T          |      |

| TX power                                       | P <sub>OUT1</sub>   | 0dBm setting                                                             | -3   | 0    | 3          | dBm  |

|                                                | P <sub>OUT2</sub>   | -18dBm setting                                                           | _    | –18  | _          | dBm  |

| Centre Frequency<br>tolerance                  | F <sub>CERR</sub>   | Master Clock tolerance < 40 ppm                                          | -40  | -    | 40         | ppm  |

| Modulation data rate                           | D <sub>RATE</sub>   | -                                                                        | -    | 1    | -          | Mbps |

| Modulation index                               | FIDX                | -                                                                        | 0.45 | 0.50 | 0.55       | -    |

| Bandwidth-bit rate<br>products BT              | BT                  | GFSK                                                                     | -    | 0.5  | -          | _    |

| F                                              | $F_{1avg}$          | Frequency deviation of 10101010 pattern                                  | 225  | 250  | 275        | kHz  |

| Modulation<br>characteristics                  | F <sub>RATE</sub>   | Frequency deviation ratio<br>between 10101010 and<br>00001111 sequence   | 80   | _    | _          | %    |

|                                                | F <sub>DELTA</sub>  | Minimum Frequency Deviation                                              | 185  | -    | -          | kHz  |

| In-band spurious                               | P <sub>OS1</sub>    | 2MHz apart from carrier<br>frequency in a 1MHz bandwidth                 | -    | -    | -20        | dBm  |

|                                                | P <sub>OS2</sub>    | 3MHz apart from carrier<br>frequency in a 1MHz bandwidth                 | _    | _    | -30        | dBm  |

| RX                                             |                     |                                                                          |      |      |            |      |

| Receiver Sensitivity                           | PSENS               | PER = 30.8% (*1)                                                         | _    | -85  | -70        | dBm  |

|                                                | Cl <sub>co</sub>    | Co-channel interference C/I                                              | 21   | _    | _          | dB   |

| Interference<br>performance                    | CI <sub>S1</sub>    | Adjacent (1MHz) interference C/I                                         | 15   | -    | -          | dB   |

| PER<30.8%<br>Wanted signal :-67dBm             | CI <sub>S2</sub>    | Adjacent (2MHz) interference C/I                                         | -17  | _    | _          | dB   |

| Interfering signal :<br>modulated signal       | CI <sub>S3</sub>    | Adjacent (>=3MHz) interference<br>C/I                                    | -27  | -    | -          | dB   |

| (*2)                                           | Cl <sub>IMG</sub>   | Image frequency interference<br>(-4MHz) C/I                              | -9   |      | _          | dB   |

|                                                | CI <sub>IMGS1</sub> | Adjacent (1MHz) interference to<br>image frequency<br>(-3MHz,-5MHz)) C/I | -15  | _    | _          | dB   |

| Out of band blocking                           | P <sub>BLK1</sub>   | 30MHz to 2000MHz BW 10MHz                                                | -30  | _    |            | dBm  |

| PER<30.8%                                      | P <sub>BLK2</sub>   | 2003 to 2399MHz BW 3MHz                                                  | -35  | _    | _          | dBm  |

| Wanted signal :-67dBm<br>Interfering signal:CW | P <sub>BLK3</sub>   | 2484 to 2997MHz BW 3MHz                                                  | -35  | _    | _          | dBm  |

| (*2) (*3)                                      | P <sub>BLK4</sub>   | 3000MHz to 12.75GHz BW 25MHz                                             | -30  | _    | _          | dBm  |

#### ML7105-002

| Intermodulation<br>PER<30.8%<br>Wanted signal :-64dBm<br>(*2) | P <sub>IM</sub>      | CW interering signal +/-3MHz<br>Modulated interfering signal<br>+/-6MHz<br>or<br>CW interfering signal +/-4MHz<br>Modulated interfering signal<br>+/-8MHz<br>or<br>CW interfering signal +/-5MHz<br>Modulated interfering signal<br>+/-10MHz | -50 | _ | _   | dBm |

|---------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|-----|-----|

| Maximum input level(*2)                                       | P <sub>RXMAX</sub>   | PER = 30.8% (*1)                                                                                                                                                                                                                             | -   | - | -10 | dBm |

| RSSI detection range                                          | P <sub>RSSIMA</sub>  | Upper                                                                                                                                                                                                                                        | -40 | - | _   | dBm |

| (*2)                                                          | P <sub>RSSIMIN</sub> | Lower                                                                                                                                                                                                                                        | _   | _ | -80 | dBm |

(\*1) PER=30.8% is corresponding to BER=0.1% (\*2) Condition: Ta = 25deg., VDDHV = 3.3V (\*3) Follow RCV-LE/CA/04/C test spec of Bluetooth SIG

#### ML7105-002

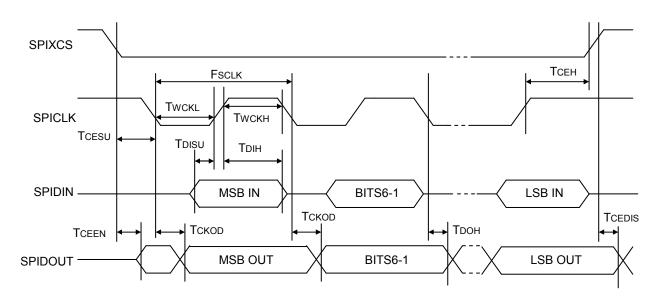

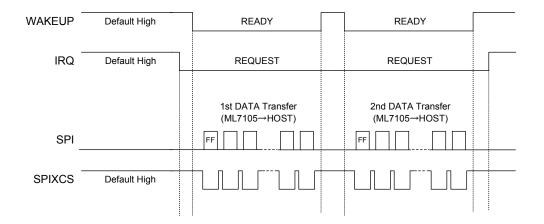

#### •SPI interface

(Ta = -20 to +70 deg.C)

| Item                               | Symbol | Condition        | Min     | Тур    | Max  | Unit |

|------------------------------------|--------|------------------|---------|--------|------|------|

| SPICLK Clock<br>Frequency          | FSCLK  |                  | 16.384  | 32.768 | 1625 | kHz  |

| SPIXCS input setup time            | TCESU  |                  | 1/Fsclk | -      | -    | ms   |

| SPIXCS input hold time             | Тсен   | Load capacitance | 1/Fsclk | -      | -    | ms   |

| SPICLK minimum high<br>pulse width | Тwскн  |                  | 250     | -      | -    | ns   |

| SPICLK minimum low pulse width     | Twckl  |                  | 250     | -      | -    | ns   |

| SPIDIN input setup time            | TDISU  |                  | 5       | -      | -    | ns   |

| SPIDIN input hold time             | TDIH   | CL=20pF          | 250     | -      | -    | ns   |

| SPICLK output delay time           | Тскор  |                  | -       | -      | 250  | ns   |

| SPIDOUT output hold time           | Трон   | -                | 5       | -      | -    | ns   |

| SPIXCS enable delay time           | TCEEN  |                  | 0       | -      | 300  | ns   |

| SPIXCS disable delay time          | TCEDIS |                  | 150     | _      | _    | ns   |

Note: When using the width of the following SPICLK edge from the data output trigger SPICLK edge within 250 ns, there is possibility that the output timing of SPIDOUT becomes simultaneous with the following edge. Consider the data input setup time of HOST and set pulse width.

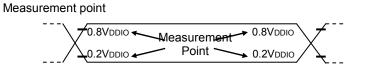

Remarks: All timing specification is defined at VDDIO x 20% and VDDIO x 80% SPIXCS input setup/hold time have to be at least 1cycle of SPICLK clock frequency

#### ML7105-002

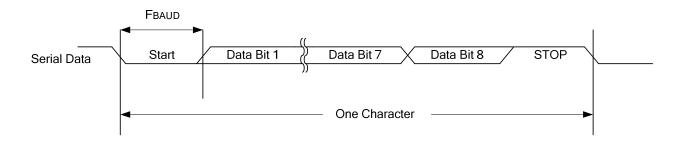

### •UART interface

(Ta = -20 to +70 deg.C)

| Item      | Symbol | Condition                   | Min | Тур   | Max | Unit        |

|-----------|--------|-----------------------------|-----|-------|-----|-------------|

| Baud Rate | Fbaud  | Load capacitance<br>CL=20pF | -   | 57600 | -   | bps(H<br>z) |

#### ML7105-002

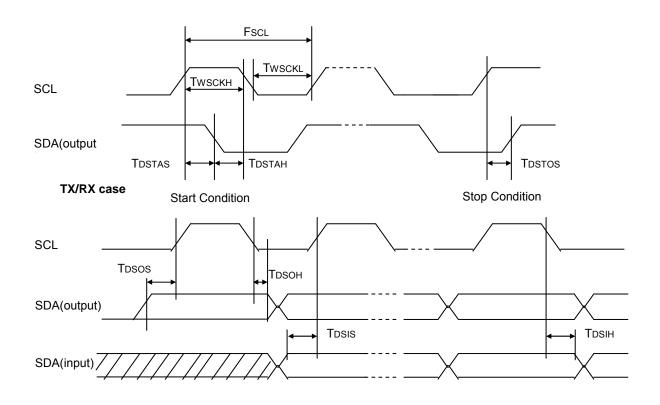

#### •I2C interface

(Ta = -20 to +70 deg.C)

| Item                         | Symbol | Condition                   | Min | Тур | Max | Unit |

|------------------------------|--------|-----------------------------|-----|-----|-----|------|

| SCL clock frequency          | Fscl   |                             | -   | -   | 400 | kHz  |

| SCL minimum high pulse width | Тwscкн | -                           | 10  | -   | -   | us   |

| SCL minimum low pulse width  | TWSCKL |                             | 10  | -   | -   | us   |

| Start condition hold time    | TDSTAH |                             | 5   | -   | -   | us   |

| Start condition setup time   | Tdstas | Load capacitance<br>CL=20pF | 5   | -   | -   | us   |

| Stop condition setup time    | TDSTOS |                             | 5   | -   | -   | us   |

| SDA output hold time         | TDSOH  |                             | 5   | -   | -   | us   |

| SCL output delay time        | TDSOS  |                             | 5   | -   | -   | us   |

| SDA input setup time         | TDSIS  |                             | 80  | -   | -   | ns   |

| SDA input hold time          | TDSIH  |                             | 0   | _   | -   | ns   |

Note: SCL clock frequency is fixed to 400kHz

#### ML7105-002

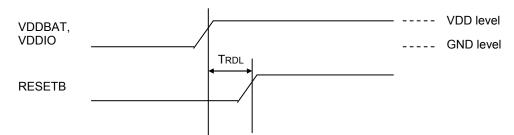

#### Reset operation

(Ta = -20 to +70 deg.C)

| Item                                           | Symbol | Condition                               | Min | Тур | Max | Unit |

|------------------------------------------------|--------|-----------------------------------------|-----|-----|-----|------|

| RESETB propagation<br>delay time<br>(Power on) | Trdl   | Start supplying power<br>(VDDBAT,VDDIO) | 20  | -   | -   | ms   |

| RESETB Pulse width                             | TRPLS  | RESETB pin                              | 1   | -   | -   | us   |

Power on reset function

Reset function from RESETB pin

It is possible to reset internal circuit by asserting RESETB after power supply is on.

It is possible to reset internal circuit by same way even if it is not power sequence. Internal circuit will move to normal state after oscillation circuit become stable by clock stabilizing circuit after reset function.

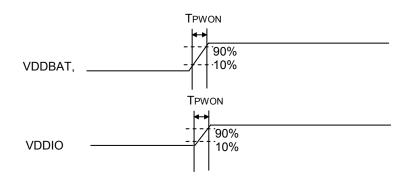

#### •Power on

(Ta = -20 to +70 deg.C)

| Item                                                        | Symbol   | Condition                                  | Min | Тур | Max | Unit |

|-------------------------------------------------------------|----------|--------------------------------------------|-----|-----|-----|------|

| VDD pin rising time                                         | Tpwon    | While power on<br>VDD pins (VDDBAT,VDDIO)  | 0.2 | 1   | 5   | ms   |

| Time difference between<br>VDD pin while power<br>on state  | TPWONdly | While power on<br>VDD pins (VDDBAT,VDDIO)  | 0   | -   | -   | ms   |

| Time difference between<br>VDD pin while power<br>off state | TPWOFdly | While power off<br>VDD pins (VDDBAT,VDDIO) | 0   | -   | -   | ms   |

ML7105-002

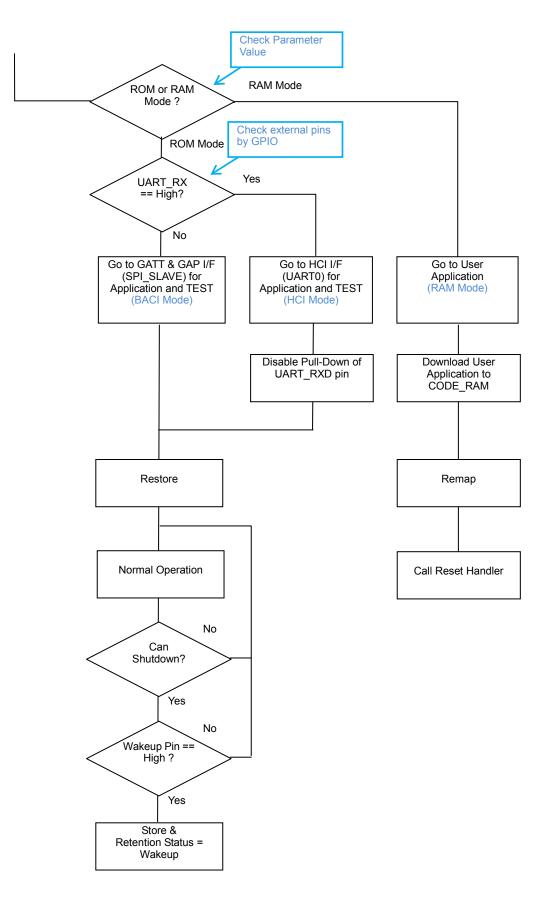

### ■Operating mode

Following 4 operating modes are available to use

| pplication mode using SPI-SLAVE interface                          |

|--------------------------------------------------------------------|

| CI mode (Bluetooth LE standard compliant) using UART interface.    |

| inction extension mode downloading user program to internal memory |

| ebugging mode to have access to I2C-EEPROM write and read.         |

|                                                                    |

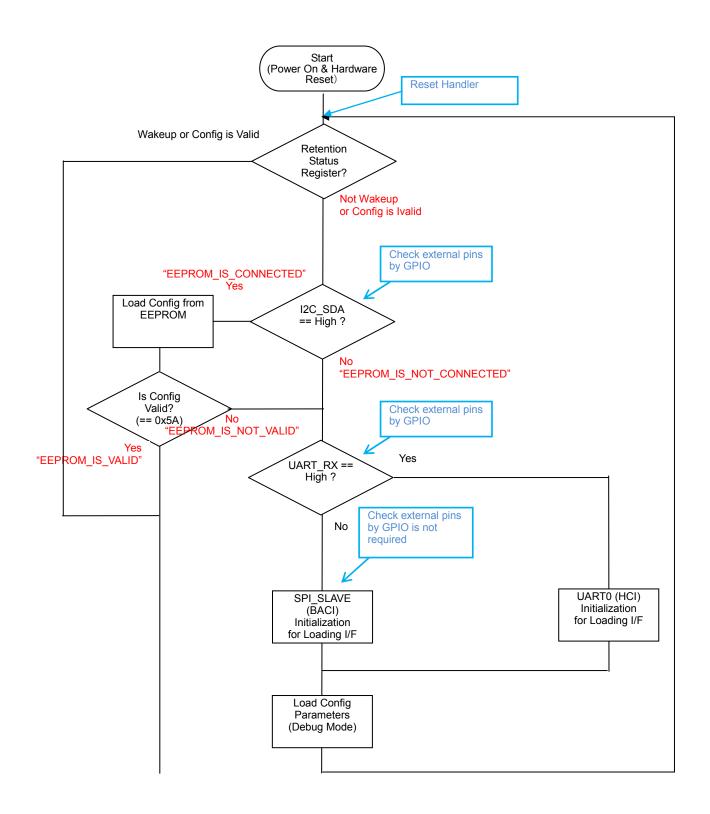

# Operating mode configuration

Configuration of operating mode will be done by pin status shown in table below. The symbol "X" is don't care, it has to be used as normal function. When configure operating mode, reset has to be issued. RAM mode and Debug mode is distinguished by configuration parameter.

| Operating mode | Pin confitions |  |

|----------------|----------------|--|

| Operating mode | UART_RXD       |  |

| BLI Mode       | Low            |  |

| HCI Mode ※1    | High           |  |

| RAM Mode       | Х              |  |

| Debug Mode     | Х              |  |

(\*) Fix Wakeup pin to Low on HCI mode.

See anootations on Section about Power State Transition

### ■Boot Sequence

Operating mode will be deciede by boot sequence shown below.

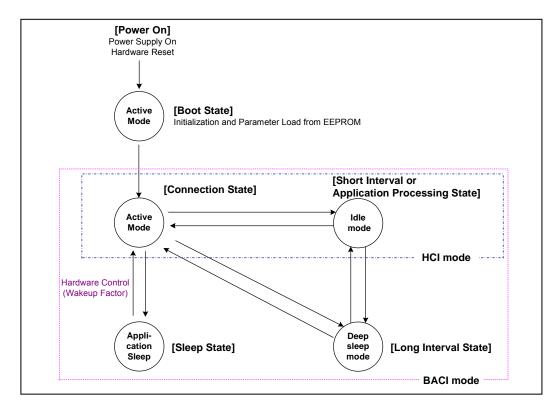

#### Power Management

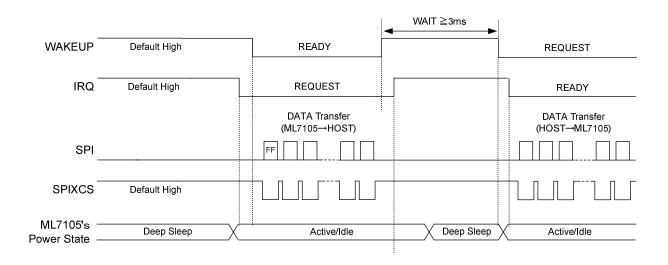

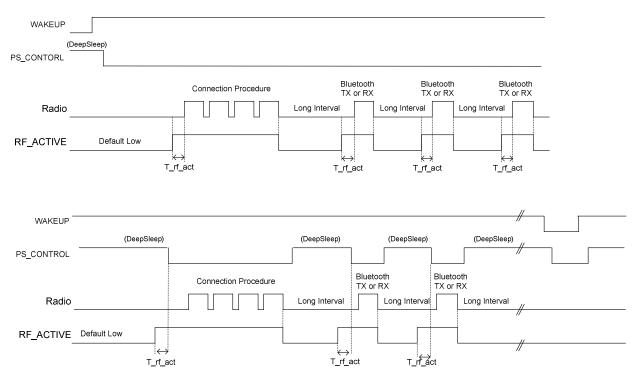

#### •Power Mode

Following Power modes are available. Active mode Idle mode Deep sleep mode Application Sleep

#### [Active mode]

Active Mode will be used during RF connection state.

#### [Idle mode]

Idle mode is low power consumption mode. It can be used between connection events with short time interval which is equal to or less than 40msec.

#### [Deep sleep mode]

Deep sleep mode will be used between connection events or system function is suspended. Oscillation block in RF block is suspeded, communication time interval will be counted by low power clock supplied from external pin.

#### [Application Sleep]

Application Sleep mode will suspend oscillation in RF block, and stand by with low power clock supplied from external pin. This is low power mode used in the case communications is unnecessary. Sleep command issue by host cpu makes become this mode, and this mode is kept till wake up from external pin.

#### • Power State Transition